# **LM148**

# **Low Power Quad 741 Operational Amplifier**

#### **Features**

- 741 op amp operating characteristics

- Low supply current drain—0.6 mA/amplifier

- Class AB output stage—no crossover distortion

- Pin compatible with the LM124

- Low input offset voltage—1.0 mV

- Low input offset current—4.0 nA

- Low input bias current—30 nA

- Unity gain bandwidth—1.0 MHz

- Channel Separation—120 dB

- Input and output overload protection

## Description

The LM148 is a true quad 741. It consists of four independent high-gain, internally compensated, low-power operational amplifiers which have been designed to provide functional characteristics identical to those of the familiar 741 operational amplifier. In addition, the total supply current for all four amplifiers is comparable to the supply current of a single 741 type op amp. Other features include input offset currents and input bias currents which are much less than those of a standard 741. Also, excellent isolation between amplifiers has been achieved by independently biasing each amplifier and using layout techniques which minimize thermal coupling.

The LM148 can be used anywhere multiple 741 type amplifiers are being used and in applications where amplifier matching or high packing density is required.

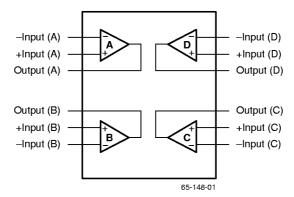

## **Block Diagram**

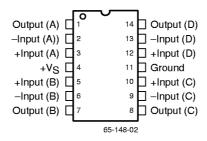

## **Pin Assignments**

# **Absolute Maximum Ratings**

| Parameter                                  | Min.       | Max. | Unit |

|--------------------------------------------|------------|------|------|

| Supply Voltage                             | -22        | +22  | V    |

| Differential Input Voltage                 |            | 44   | V    |

| Input Voltage <sup>1</sup>                 | -22        | +22  | V    |

| Output Short Circuit Duration <sup>2</sup> | Indefinite |      |      |

| Storage Temperature Range                  | -65        | +150 | °C   |

| Operating Temperature Range                | -55        | +125 | °C   |

| Lead Soldering Temperature (60 sec.)       | +300°C     |      |      |

#### Notes:

- 1. For supply voltages less than ±15V, the absolute maximum input voltage is equal to the supply voltage.

- 2. Short circuit to ground on one amplifier only.

### **Thermal Characteristics**

| Parameter                           | 14-Lead Ceramic DIP |

|-------------------------------------|---------------------|

| Maximum Junction Temperature        | +175°C              |

| Maximum PD TA < 50°C                | 1042 mW             |

| Thermal Resistance, θJC             | 60°C/W              |

| Thermal Resistance, θJA             | 120°C/W             |

| For T <sub>A</sub> > 50°C derate at | 8.33 mW/°C          |

## **Electrical Characteristics**

(Vs =  $\pm 15$ V and TA = 25°C, unless otherwise noted)

| Parameter                                         | Test Conditions                                            |                            | Min. | Тур. | Max. | Unit    |

|---------------------------------------------------|------------------------------------------------------------|----------------------------|------|------|------|---------|

| Input Offset Voltage                              | R <sub>S</sub> ≤ 10KΩ                                      |                            |      | 1.0  | 5.0  | mV      |

| Input Offset Current                              |                                                            |                            |      | 4.0  | 25   | nA      |

| Input Bias Current                                |                                                            |                            |      | 30   | 100  | nA      |

| Input Resistance (Differential Mode) <sup>1</sup> |                                                            |                            | 0.8  | 2.5  |      | ΜΩ      |

| Supply Current, All Amplifiers                    | Vs = ±15V                                                  | Vs = ±15V                  |      | 2.4  | 3.6  | mA      |

| Large Signal Voltage Gain                         | $V_S = \pm 15V$ , $V_{OUT} = \pm 10V$ , $R_L \ge 2K\Omega$ |                            | 50   | 160  |      | V/mV    |

| Channel Separation                                | F = 1 Hz 20 KHz                                            |                            |      | 120  |      | dB      |

| Unity Gain Bandwidth                              |                                                            |                            |      | 1.0  |      | MHz     |

| Phase Margin                                      |                                                            |                            |      |      | 60   | Degrees |

| Slew Rate                                         |                                                            |                            |      |      | 0.5  | V/µS    |

| Short Circuit Current                             |                                                            |                            |      | 25   |      | mA      |

| The following specifications apply fo             | or Vs = ±15V, -55°                                         | °C ≤T <sub>A</sub> ≤ +125° | C.   |      | •    | •       |

| Input Offset Voltage                              | Rs ≤ 10KΩ                                                  | Rs ≤ 10KΩ                  |      |      | 6.0  | mV      |

| Input Offset Current                              |                                                            |                            |      |      | 75   | nA      |

| Input Bias Current                                |                                                            |                            |      |      | 325  | nA      |

| Large Signal Voltage Gain                         | $V_S = \pm 15V$ , $V_{OUT} = 10V$ , $R_L < 2K\Omega$       |                            | 25   |      |      | V/mV    |

| Output Voltage Swing                              | Vs = ±15V                                                  | R <sub>L</sub> = 10KΩ      | ±12  | ±13  |      | V       |

|                                                   |                                                            | $R_L = 2K\Omega$           | ±10  | ±12  |      | 1       |

| Input Voltage Range                               | Vs = ±15V                                                  |                            | ±12  |      |      | V       |

| Common Mode Rejection Ratio                       | Rs ≤ 10KΩ                                                  |                            | 70   | 90   |      | dB      |

| Power Supply Rejection Ratio                      | R <sub>S</sub> ≤ 10KΩ                                      |                            | 77   | 96   |      | dB      |

<sup>1.</sup> Guaranteed by design but not tested.

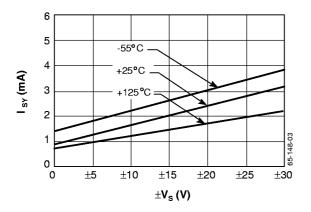

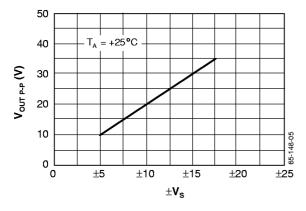

## **Typical Performance Characteristics**

Figure 1. Supply Current vs. Supply Voltage

Figure 3. Output Voltage Swing vs. Supply Voltage

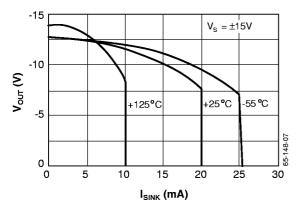

Figure 5. Negative Current Limit

Output Voltage vs. Output Sink Current

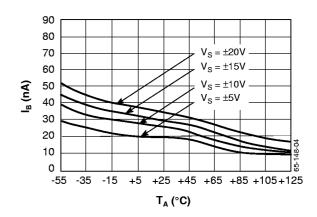

Figure 2. Input Bias Current vs. Temperature

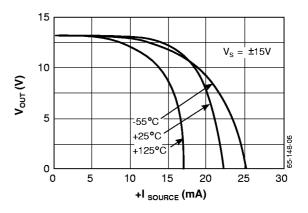

Figure 4. Positive Current Limit

Output Voltage vs. Output Source Current

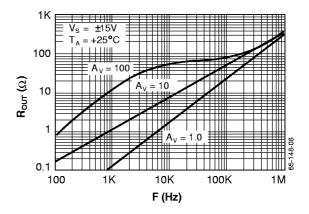

Figure 6. Output Impedance vs. Frequency

## Typical Performance Characteristics (continued)

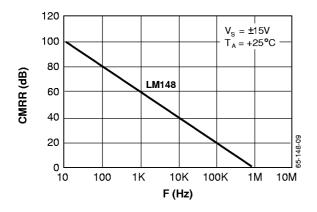

Figure 7. CMRR vs. Frequency

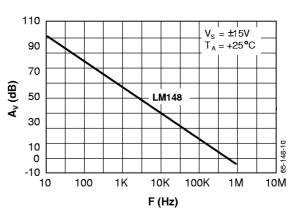

Figure 8. Open Loop Gain vs. Frequency

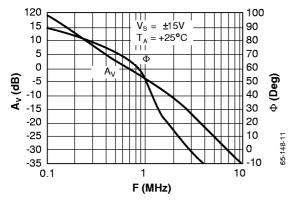

Figure 9. Gain, Phase vs. Frequency

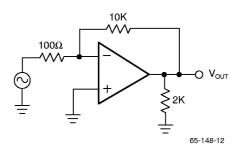

Figure 10. Gain, Phase Test Circuit

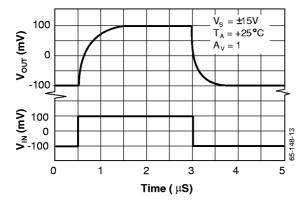

Figure 11. Small Signal Pulse Response Input, Output Voltage vs. Time

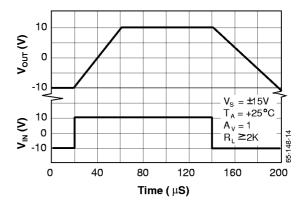

Figure 12. Large Signal Pulse Response Output Voltage vs. Time

## Typical Performance Characteristics (continued)

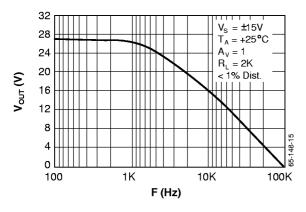

Figure 13. Undistorted Output Voltage Swing vs. Frequency

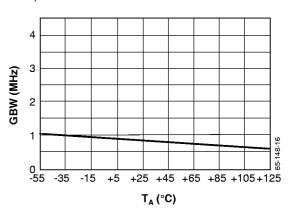

Figure 14. Gain Bandwidth Product vs. Temperature

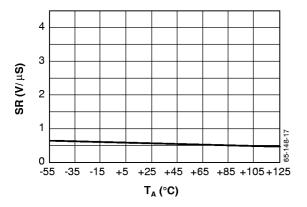

Figure 15. Slew Rate vs. Temperature

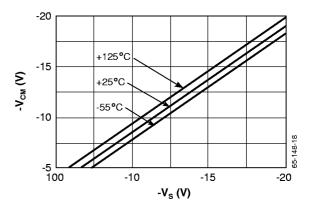

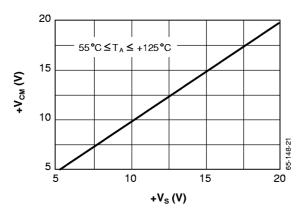

Figure 16. Negative Common Mode Input Voltage vs. Supply Voltage

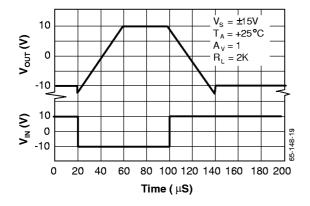

Figure 17. Inverting Large Signal Pulse Response Input, Output Voltage vs. Time

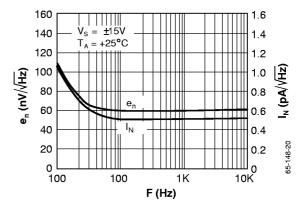

Figure 18. Input Noise Voltage, Current Densities vs. Frequency

# **Typical Performance Characteristics** (continued)

Figure 19. Positive Common Mode, Input Voltage vs. Supply Voltage

# **Typical Simulation**

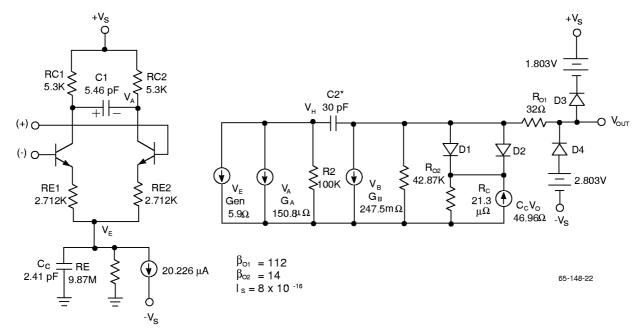

Figure 20. LM148 Macromodel for Computer Simulation

## **Applications Discussion**

The LM148 low power quad operational amplifier exhibits performance comparable to the popular 741. Substitution can therefore be made with no change in circuit behavior.

The input characteristics of these devices allow differential voltages which exceed the supplies. Output phase will be correct as long as one of the inputs is within the operating common mode range. If both exceed the negative limit, the output will latch positive. Current limiting resistors should be used on the inputs in case voltages become excessive.

When capacitive loading becomes much greater than 100pF, a resistor should be placed between the output and feedback connection in order to reduce phase shift.

The LM148 is short circuit protected to ground and supplies continuously when only one of the four amplifiers is shorted. If multiple shorts occur simultaneously, the unit can be destroyed due to excessive power dissipation.

To assure stability and to minimize pickup, feedback resistors should be placed close to the input to maximize the feedback pole frequency (a function of input to ground capacitance). A good rule of thumb is that the feedback pole frequency should be 6 times the operating -3.0B frequency. If less, a lead capacitor should be placed between the output and input.

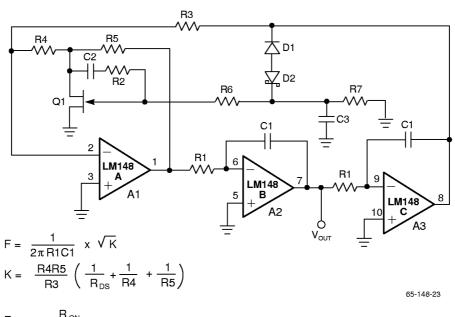

$R_{DS} \cong \frac{R_{ON}}{\left(1 - \frac{V_{GS}}{V_{P}}\right)^{1/2}}$

F<sub>MAX</sub> = 5.0 KHz, THD≤ 0.03%

R1 = 100K pot., C1 =  $0.0047 \, \mu F$ , C2 =  $0.01 \, \mu F$ , C3 =  $0.1 \, \mu F$ , R2 = R6 = R7 = 1M, R3 =  $5.1 \, K$ , R4 =  $12 \Omega$ .

R5 = 240 Ω, Q1 = NS5102, D1 = 1N914, D2 = 3.6V avalanche diode (ex. LM103),  $V_S = \pm 15V$

A simpler version with some distortion degradation at high frequencies can be made by using A1 as a simple inverting amplifier, and by putting back to back zeners in feedback loop of A3.

Figure 21. One Decade Low Distortion Sinewave Generator

## **Applications Discussion** (continued)

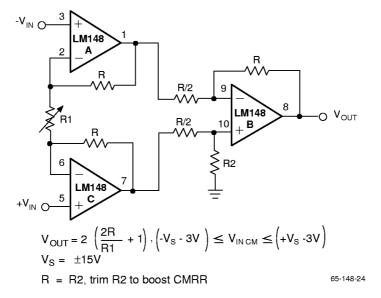

Figure 22. Low Cost Instrumentation Amplifier

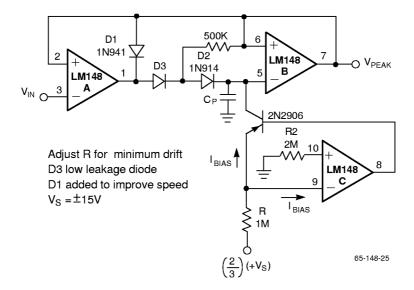

Figure 23. Low Voltage Peak Detector with Bias Current Compensation

## **Applications Discussion** (continued)

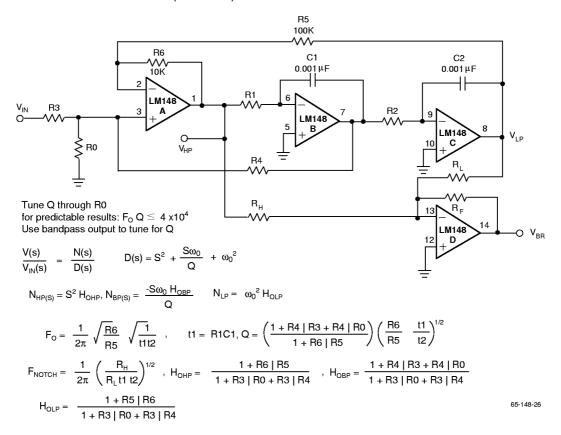

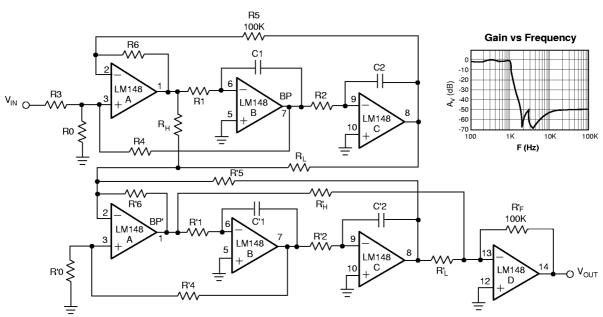

Figure 24. Universal State-Space Filter

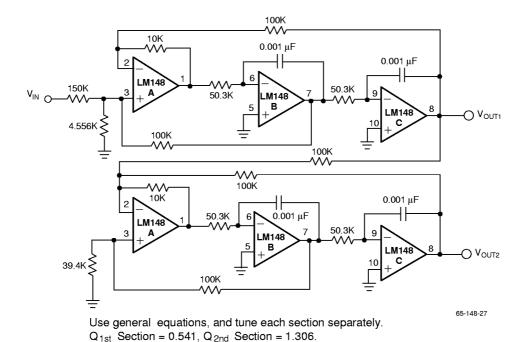

Figure 25. 1 KHz 4-Pole Butterworth Filter

The response should have 0 dB peaking.

## **Applications Discussion** (continued)

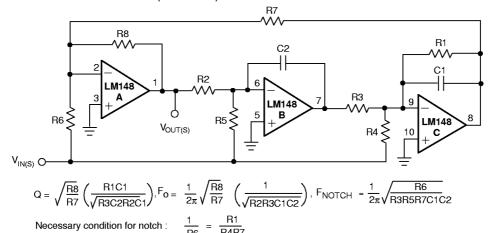

Examples:  $F_{NOTCH} = 3 \text{ kHz}$ , Q = 5, R1 = 270 K, R2 = R3 = 20 K, R4 = 27 K, R5 = 20 K, R6 = R8 = 10 K, R7 = 100 K.  $C1 = C2 = 0.001 \, \mu\text{F}$ .

Better noise performance than the state-space approach.

65-148-28

Figure 26. 3 Amplifier Bi-Quad Notch Filter

$F_C$  = 1 kHz,  $F_S$  = 2 kHz,  $F_P$  = 0.543.  $F_Z$  = 2.14, Q = 0.841,  $F'_P$  = 0.987,  $F'_Z$  = 4.92. Q' = 4.403 normalized to ripple BW.

$$F_p = -\frac{1}{2^T}\sqrt{\frac{R6}{R5}} - \left(\frac{1}{t}\right), \ F_Z = \frac{1}{2^T}\sqrt{\frac{R_H}{R_L}}\left(\frac{1}{t}\right), \ Q = -\frac{1 + R4/R3 + R4/R0}{1 + R6/R5} - x \sqrt{\frac{R6}{R5}} - x \sqrt{\frac{R'6}{R'5}} - x \sqrt{\frac{1 + R'4/R'0}{1 + R'6/R'5 + R'6/R'5}}$$

$$R_{p} = \frac{R_{H}R_{L}}{R_{H} + R_{I}}$$

Use the B'P outputs to tune Q, Q', tune the 2 sections separately. R1 = R2 = 92.6K, R3 = R4 = R5 = 100K, R6 = 10K, R0 = 107.8K,  $R_L = 100K$ ,  $R_H = 155.1K$ , R'1 = R'2 = 50.9K, R'4 = R'5 = 100K, R'6 = 10K, R'0 = 5.78K,  $R'_L = 100K$ ,  $R'_H = 248.12K$ ,  $R'_F = 100K$ .

65-148-29

All capacitors are  $0.001 \mu F$ .

Figure 27. 4th Order 1 KHz Elliptic Filter (4 Poles, 4 Zeros)

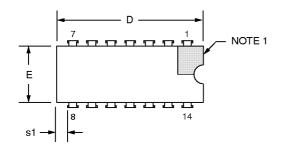

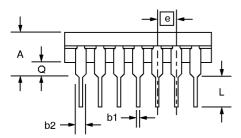

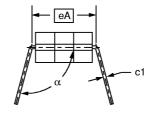

### **Mechanical Dimensions**

#### 14-Pin Ceramic DIP

| Symbol | Inches   |      | Millimeters |       | Notes |

|--------|----------|------|-------------|-------|-------|

| Symbol | Min.     | Max. | Min.        | Max.  | Notes |

| Α      | _        | .200 | _           | 5.08  |       |

| b1     | .014     | .023 | .36         | .58   | 8     |

| b2     | .045     | .065 | 1.14        | 1.65  | 2     |

| c1     | .008     | .015 | .20         | .38   | 8     |

| D      |          | .785 |             | 19.94 | 4     |

| Е      | .220     | .310 | 5.59        | 7.87  | 4     |

| е      | .100 BSC |      | 2.54 BSC    |       | 5, 9  |

| eA     | .300 BSC |      | 7.62 BSC    |       | 7     |

| L      | .125     | .200 | 3.18        | 5.08  |       |

| Ø      | .015     | .060 | .38         | 1.52  | 3     |

| s1     | .005     | _    | .13         | _     | 6     |

| α      | 90°      | 105° | 90°         | 105°  |       |

- Index area: a notch or a pin one identification mark shall be located adjacent to pin one. The manufacturer's identification shall not be used as pin one identification mark.

- 2. The minimum limit for dimension "b2" may be .023 (.58mm) for leads number 1, 7, 8 and 14 only.

- 3. Dimension "Q" shall be measured from the seating plane to the base plane.

- 4. This dimension allows for off-center lid, meniscus and glass overrun.

- 5. The basic pin spacing is .100 (2.54mm) between centerlines. Each pin centerline shall be located within  $\pm$ .010 (.25mm) of its exact longitudinal position relative to pins 1 and 14.

- 6. Applies to all four corners (leads number 1, 7, 8, and 14).

- 7. "eA" shall be measured at the center of the lead bends or at the centerline of the leads when " $\alpha$ " is 90°.

- 8. All leads Increase maximum limit by .003 (.08mm) measured at the center of the flat, when lead finish applied.

- 9. Twelve spaces.

## **Ordering Information**

| Part Number | Package             | Operating Temperature<br>Range |

|-------------|---------------------|--------------------------------|

| LM148D      | 14-Lead Ceramic DIP | -55°C to +125°C                |

| LM148D/883B | 14-Lead Ceramic DIP | -55°C to +125°C                |

#### Note:

1. 883B suffix denotes Mil-Std-883, Level B processing

The information contained in this data sheet has been carefully compiled; however, it shall not by implication or otherwise become part of the terms and conditions of any subsequent sale. Raytheon's liability shall be determined solely by its standard terms and conditions of sale. No representation as to application or use or that the circuits are either licensed or free from patent infringement is intended or implied. Raytheon reserves the right to change the circuitry and any other data at any time without notice and assumes no liability for errors.

### LIFE SUPPORT POLICY:

Raytheon's products are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of Raytheon components in life support applications assumes all risk of such use and indemnifies Raytheon Company against all damages

Raytheon Electronics Semiconductor Division 350 Ellis Street Mountain View, CA 94043 650.968.9211 FAX 650.966.7742