AN-009 HiRel Power Application Brief

PCB Layout Considerations with GaN E-HEMTs

October 23, 2020

#### **Overview**

- This guide provides an overview of the good engineering practice for PCB layout of designs using GaN Systems' embedded GaNPX® packaged E-HEMTs.

- Layout guidelines are introduced for the following four circuit configurations

- 1) Isolated gate driver circuit for single GaN E-HEMTs

- 2) Isolated gate driver circuit for paralleled GaN E-HEMTs

- 3) Half-bridge Booststrap gate driver circuit

- 4) EZDrive<sup>SM</sup> circuit

- With optimum board layout combined with low GaNPX® package inductance, GaN E-HEMTs exhibit optimum switching performance

#### Introduction

- GaN Systems' E-HEMTs have very low packaging inductance, while enabling ultra-low inductance PCB power loops.

- Good engineering practice of layout techniques are required to minimize parasitic inductance and fully utilize the benefit of GaN Systems' E-HEMTs.

- This application note shows key steps to design an optimal PCB layout with GaN to maximize converter performance.

#### **Motivation**

- GaN E-HEMTs switch much faster than Si MOSFETs, and require proper engineering consideration of PCB layout design to minimize parasitic inductances.

- Parasitic inductances can cause higher overshoot voltages, ringing/oscillation, EMC issues, which can lead to overstressing the E-HEMTs.

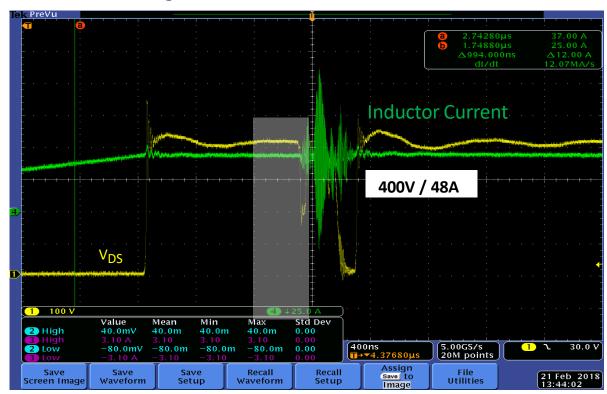

Example of an unsuccessful design caused by unbalanced quasi-common source inductance

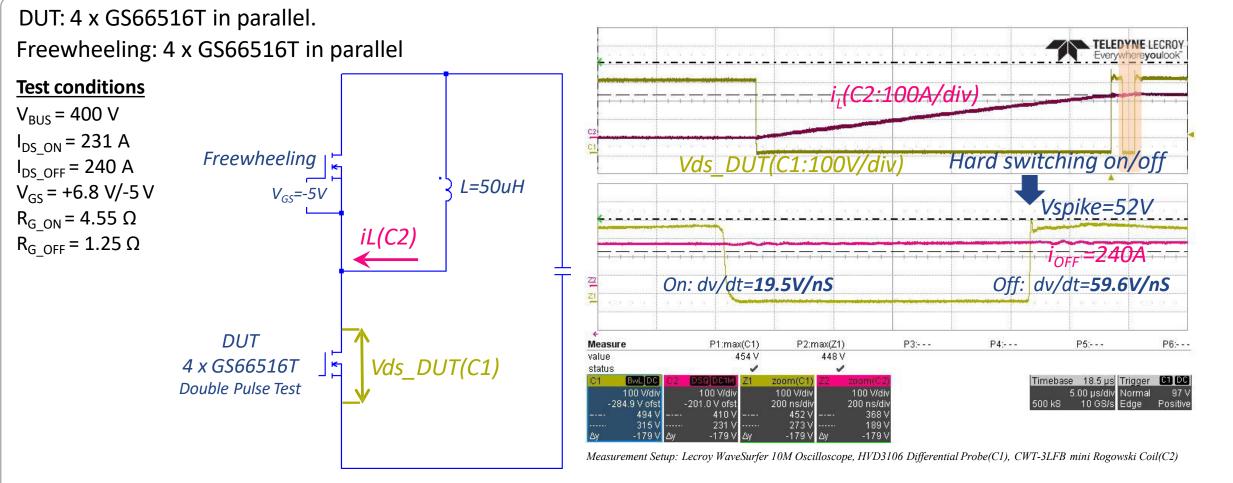

Measurement Setup: Lecroy WaveSurfer 10M Oscilloscope, HVD3106 Differential Probe(C1), CWT-3LFB mini Rogowski Coil(C2)

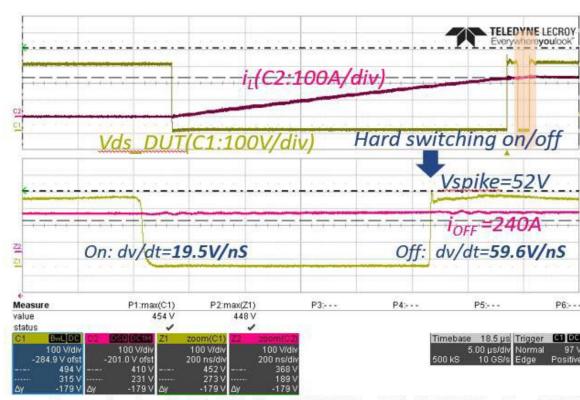

Example of clean switching waveforms when good PCB layout practices are used (400 V/240 A DPT)

#### **PCB Layout Steps**

- Step 1: Prepare the schematics and identify the components of each critical loop

- Isolated gate driver circuit for single GaN HEMTs

- Isolated gate driver circuit for paralleled GaN HEMTs

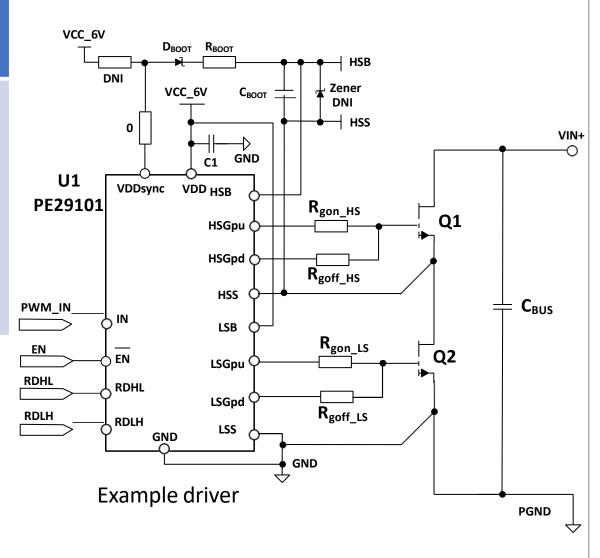

- Half-bridge Bootstrap gate driver circuit

- EZDrive<sup>SM</sup> circuit

- Step 2: Place the components according to the design priority and current direction

- Put components as close as possible

- According to the current direction, set the component in sequence

- If there is a conflict for minimizing all the loops, refer to the priority listed on slides 7/8/9/10.

- Step 3: Connect the components optimally to achieve low parasitics with flux cancellation techniques

#### **PCB Layout Steps**

- Step 1: Prepare the schematics and identify the components of each critical loop

- Isolated gate driver circuit for single GaN HEMTs

- Isolated gate driver circuit for paralleled GaN HEMTs

- Half-bridge Bootstrap gate driver circuit

- EZDrive<sup>SM</sup> circuit

- Step 2: Place the components according to the design priority and current direction

- Put components as close as possible

- According to the current direction, set the component in sequence

- If there is a conflict for minimizing all the loops, refer to the priority listed on slides 7/8/9/10.

- Step 3: Connect the components optimally to achieve low parasitics with flux cancellation techniques

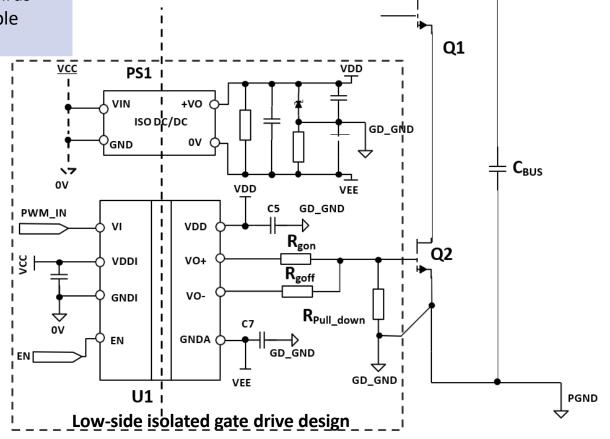

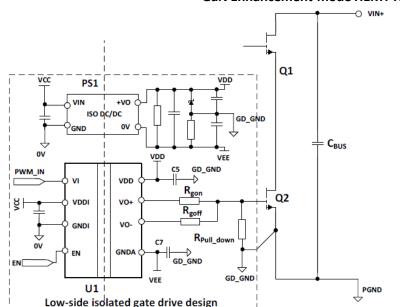

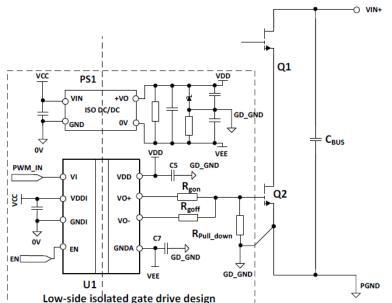

## Isolated gate driver circuit for single GaN HEMT

| Priority | Critical Loops                 | Components                  | Critical Loops<br>Design Rule |

|----------|--------------------------------|-----------------------------|-------------------------------|

| 1        | Power Commutation loop         | Q1,Q2,C <sub>BUS</sub>      |                               |

| 2a       | LS Gate Driver loop (turn-on)  | C5,U1,R <sub>gon</sub> ,Q2  | As small as                   |

| 2b       | LS Gate Driver loop (turn-off) | C7,U1,R <sub>goff</sub> ,Q2 | possible                      |

- High-side isolated gate drive design is symmetric as Low-side, not shown in the diagram

- Priority of HS gate driver loop is same as LS

**GaN Enhancement-mode HEMT Half Bridge**

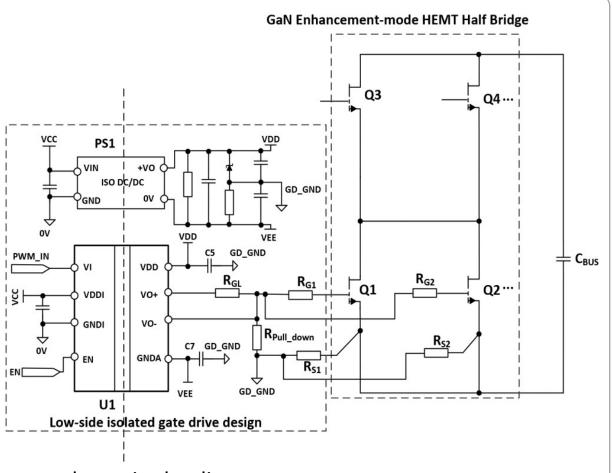

## Isolated gate driver circuit for paralleled GaN HEMTs

| Priority   | Critical Loops                       | Components                                                                                   | Critical Loops<br>Design Rule                                    |

|------------|--------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| <b>1</b> a | Quasi-common source loop (high-side) | Q3, Q4                                                                                       |                                                                  |

| 1b         | Quasi-common source loop (low-side)  | Q1, Q2                                                                                       | As small and                                                     |

| 2          | Power Commutation loop               | C <sub>BUS</sub> , Q3/Q4,<br>Q1/Q2                                                           | symmetric for<br>each of<br>paralleled<br>devices as<br>possible |

| 3a         | LS Gate Driver loop<br>(turn-on)     | C5, U1, RGL,<br>R <sub>G1</sub> /Q1/R <sub>S1</sub> ,<br>R <sub>G2</sub> /Q2/R <sub>S2</sub> |                                                                  |

| 3b         | LS Gate Driver loop<br>(turn-off)    | C7, U1,<br>R <sub>G1</sub> /Q1/R <sub>S1</sub> ,<br>R <sub>G2</sub> /Q2/R <sub>S2</sub>      |                                                                  |

- High-side isolated gate drive design is symmetric as Low-side, not shown in the diagram

- Priority of HS gate driver loop is same as LS

- Distributed gate and source resistance  $R_{G1}/R_{G2}$  and  $R_{S1}/R_{S2}$  needs to be separated

## **Half-bridge Bootstrap Gate Driver Circuit (Non-isolated)**

| Priority | Critical Loops                    | Components                                                    | Critical<br>Loops<br>Design Rule |

|----------|-----------------------------------|---------------------------------------------------------------|----------------------------------|

| 1        | Power Commutation loop            | Q1, Q2, C <sub>BUS</sub>                                      |                                  |

| 2a       | HS Gate Driver Loop<br>(turn-on)  | $D_{BOOT}$ , $R_{BOOT}$ , $C_{BOOT}$ , U1, $R_{gon\_HS}$ , Q1 |                                  |

| 2b       | HS Gate Driver Loop<br>(turn-off) | Q1, R <sub>goff_HS</sub> , U1                                 | As small as                      |

| 2c       | LS Gate Driver Loop<br>(turn-on)  | C1, U1, R <sub>gon_LS</sub> , Q2                              | possible                         |

| 2d       | LS Gate Driver Loop<br>(turn-off) | Q2, R <sub>goff_LS</sub> , U1                                 |                                  |

Use above table to identify critical loop, components and priority

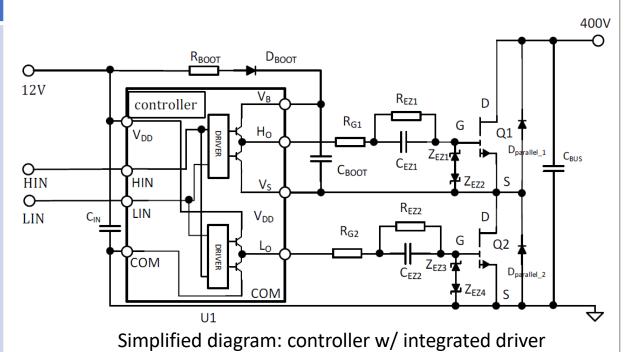

## **EZDrive**<sup>SM</sup> circuit (Non-isolated half-bridge)

| Priority   | Critical Loops                    | Components                                                                                                    | Critical<br>Loops<br>Design Rule |

|------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1          | Power Commutation<br>Loop         | Q1, Q2, C <sub>BUS</sub>                                                                                      |                                  |

| <b>2</b> a | HS Gate Driver Loop<br>(turn-on)  | $R_{BOOT}$ , $D_{BOOT}$ , $C_{BOOT}$ , $U1$ , $R_{G1}$ , $R_{EZ1}$ , $C_{EZ1}$ , $Z_{EZ1}$ , $Z_{EZ2}$ , $Q1$ |                                  |

| 2b         | HS Gate Driver Loop<br>(turn-off) | Q1, $Z_{EZ1}$ , $Z_{EZ2}$ , $R_{EZ1}$ , $C_{EZ1}$ , $R_{G1}$ , U1                                             | As small as possible             |

| 2c         | LS Gate Driver Loop<br>(turn-on)  | U1, $R_{G2}$ , $R_{EZ2}$ , $C_{EZ2}$ , $Z_{EZ3}$ , $Z_{EZ4}$ , Q2                                             |                                  |

| 2d         | LS Gate Driver Loop<br>(turn-off) | Q2, $Z_{EZ3}$ , $Z_{EZ4}$ , $R_{EZ2}$ , $C_{EZ2}$ , $R_{G2}$ , U1                                             |                                  |

Use above table to identify critical loop, components and priority

Note: more details about EZDrive<sup>SM</sup> is available from the link:

https://gansystems.com/wp-content/uploads/2018/12/GN010-EZDrive-Solution-for-GaN-Systems-E-HEMTs- 20181221.pdf

October 2020

### **PCB Layout Steps**

- Step 1: Prepare the schematics and identify the components of each critical loop

- Isolated gate driver circuit for single GaN HEMTs

- Isolated gate driver circuit for paralleled GaN HEMTs

- Half-bridge Bootstrap gate driver circuit

- EZDrive<sup>SM</sup> circuit

- Step 2: Place the components according to the design priority and current direction

- Put components as close as possible

- According to the current direction, set the component in sequence

- If there is a conflict for minimizing all the loops, refer to the priority listed on slides 7/8/9/10.

- Step 3: Connect the components optimally to achieve low parasitics with flux cancellation techniques

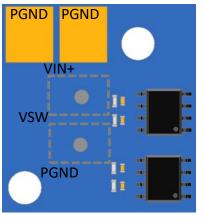

## **Step 2.1: Power commutation loops (Top-side cooling)**

# **Step 2.2: Gate Driver Circuit Loop (Top-side cooling)**

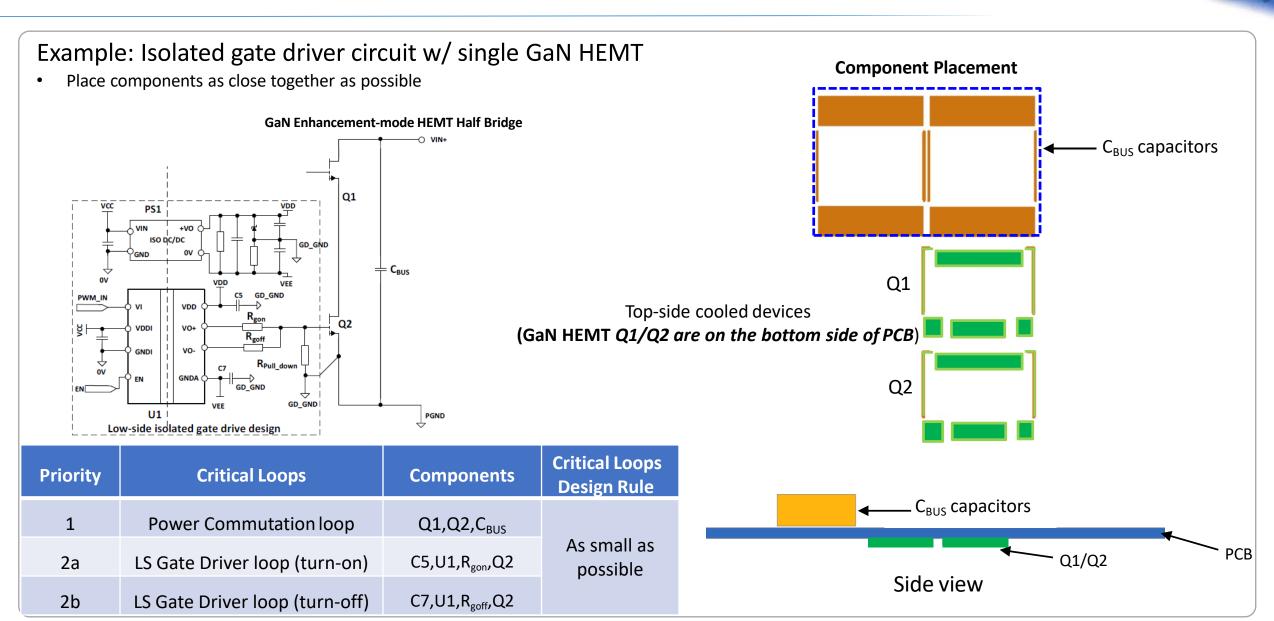

### Example: Isolated gate driver circuit w/ single GaN HEMT

- Locate drivers close to the gate

- Use/create kelvin source for driver return

Top-side cooled devices

(GaN HEMT Q1/Q2 are on the bottom side of PCB)

| Priority | Critical Loops                 | Components                  | Critical Loops Design Rule |

|----------|--------------------------------|-----------------------------|----------------------------|

| 1        | Power Commutation loop         | Q1,Q2,C <sub>BUS</sub>      |                            |

| 2a       | LS Gate Driver loop (turn-on)  | C5,U1,R <sub>gon</sub> ,Q2  | As small as possible       |

| 2b       | LS Gate Driver loop (turn-off) | C7,U1,R <sub>goff</sub> ,Q2 | 1 3 3 3 3 3 3              |

**Component Placement**

Q1

Q2

October 2020

C<sub>BUS</sub> capacitors

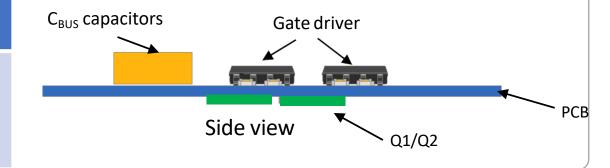

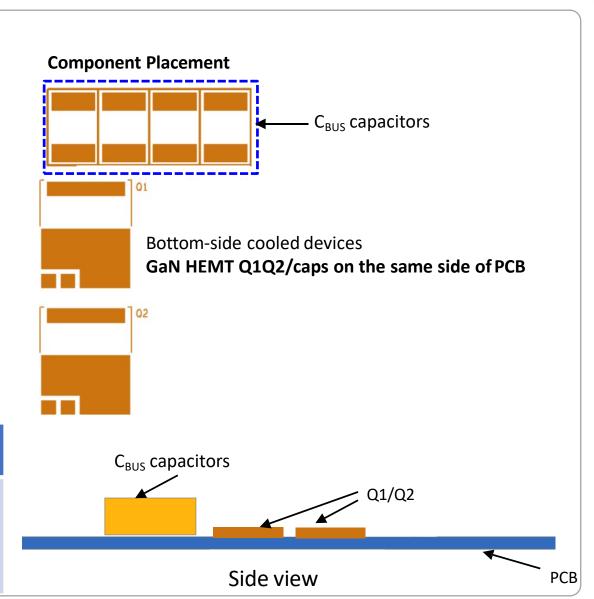

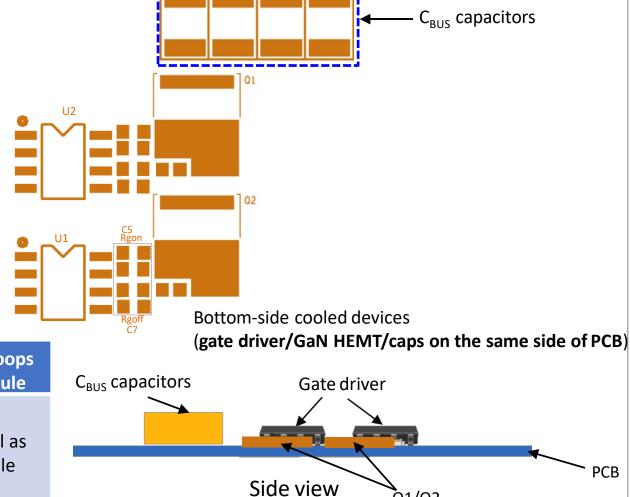

## **Step 2.1: Power commutation loops (Bottom-side cooling)**

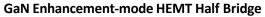

#### Example: Isolated gate driver circuit w/ single GaN HEMT

Place components as close together as possible

| Priority | Critical Loops                 | Components                  | Critical Loops<br>Design Rule |

|----------|--------------------------------|-----------------------------|-------------------------------|

| 1        | Power Commutation loop         | Q1,Q2,C <sub>BUS</sub>      |                               |

| 2a       | LS Gate Driver loop (turn-on)  | C5,U1,R <sub>gon</sub> ,Q2  | As small as possible          |

| 2b       | LS Gate Driver loop (turn-off) | C7,U1,R <sub>soff</sub> ,Q2 | p = 33.0.0                    |

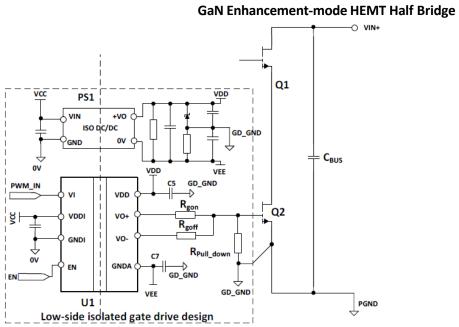

## **Step 2.2: Gate Driver Circuit Loop (Bottom-side cooling)**

#### Example: Isolated gate driver circuit with single GaN HEMT

- Locate drivers close to the gate

- Use/create kelvin source for driver return

#### **GaN Enhancement-mode HEMT Half Bridge**

| Priority | Critical Loops                 | Components                  | Critical Loops<br>Design Rule |

|----------|--------------------------------|-----------------------------|-------------------------------|

| 1        | Power Commutation loop         | Q1,Q2,C <sub>BUS</sub>      |                               |

| 2a       | LS Gate Driver loop (turn-on)  | C5,U1,R <sub>gon</sub> ,Q2  | As small as possible          |

| 2b       | LS Gate Driver loop (turn-off) | C7,U1,R <sub>goff</sub> ,Q2 | p = 30.0.0                    |

**Component Placement**

Q1/Q2

### **PCB Layout Steps**

- Step 1: Prepare the schematics and identify the components of each critical loop

- Isolated gate driver circuit for single GaN HEMTs

- Isolated gate driver circuit for paralleled GaN HEMTs

- Half-bridge Bootstrap gate driver circuit

- EZDrive<sup>SM</sup> circuit

- Step 2: Place the components according to the design priority and current direction

- Put components as close as possible

- According to the current direction, set the component in sequence

- If there is a conflict for minimizing all the loops, refer to the priority listed on slides 7/8/9/10.

- Step 3: Connect the components optimally to achieve low parasitics with flux cancellation techniques

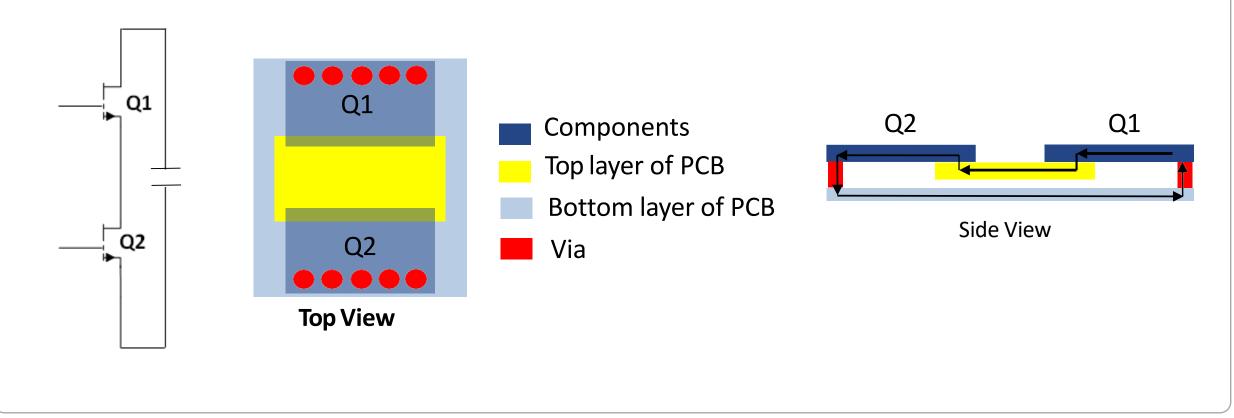

### **Step 3.1: Introduction - Magnetic Flux Cancellation for Lower Inductance**

- When two adjacent conductors are located close with opposite current direction, magnetic flux generated by two current flows will cancel each other.

- This magnetic flux canceling effect can lower the parasitic inductance.

- Arrange the layout so that high-frequency current flows in opposite direction on two adjacent PCB layers.

October 2020

### **Step 3.2: Connect the components with Flux-cancelling traces**

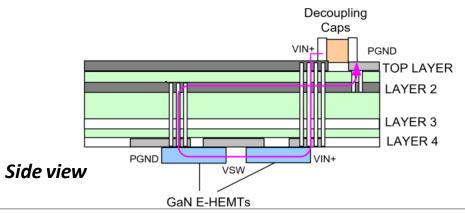

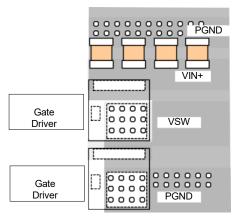

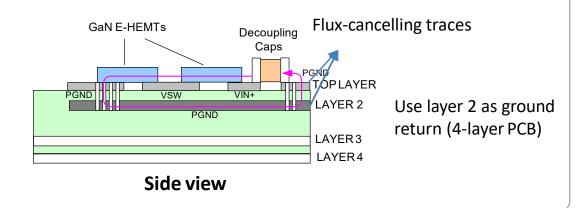

Connect the components with Flux-cancelling traces, see below example of top-side cooled devices and bottom-side cooled devices.

Example: Top-side cooled devices (GaN HEMT is on the bottom side of PCB)

Q1 Q2

Top view

**Bottom view**

Example: Bottom-side cooled devices (gate driver/GaN HEMT/caps on the same side of PCB)

Top view

October 2020

## **Experimental Example: 400V/240A DPT Hard-switching Test**

- Using good engineering practice for PCB layout in designs where GaN Systems' E-HEMTs are paralleled, current balancing and clean switching can be achieved. Hard switched is possible to full rated current.

- This example demonstrates ~200V V<sub>DS</sub> margin on a 400V/240A hard-switching test

## **Summary**

- Due to faster switching speed of GaN E-HEMTs, good engineering practice for PCB layout techniques are required to minimize parasitic inductance and fully utilize these advanced devices.

- Optimizing the PCB layout is important to achieve the maximum performance capability of GaN based designs. With optimum board layout combined with low GaN*PX*® package inductance, GaN Systems' E-HEMTs exhibit peak switching performance.

www.tdehirel.com

www.gansystems.com