February 2021

# TD72403L10DB

## CMOS PARALLEL FIFO 64 x 4-BIT, 10 MHZ

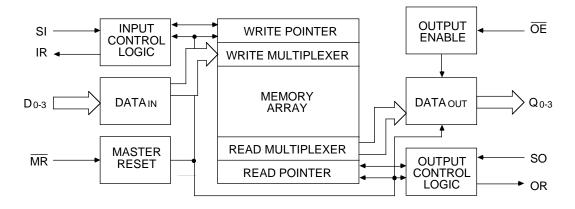

## **Functional Description**

The TD72403 is an asynchronous, high performance First-In/First-Out (FIFO) memory organized 64 words by 4 bits. The IDT72403 has an Output Enable (OE) pin. The FIFO accepts 4-bit data at the data input (D0-D3). The stored data is stacked on a first-in/ firstout basis.

The Shift Out (SO) signal causes the data at the next to last word to be shifted to the output while all other data moves down one location in the stack. The Input Ready (IR) signal functions as a flag indicating when the input is ready for new data (IR = HIGH) or to signal when the FIFO stack is full (IR = LOW).

The Output Ready (OR) signal functions as a flag indicating that the output remains valid data (OR = HIGH) or indicating that the FIFO is empty (OR = LOW). Reading and writing operations are completely asynchronous allowing the FIFO to be used as a buffer between two digital machines of widely varying operating frequencies. The 10 MHz speed makes these FIFOs ideal for high-speed communication and controller applications.

This military grade product is manufactured in compliance with the latest revision of MIL-PRF-38535, Class level B.

## Features

- First-In/First-Out Dual-Port memory

- 64 x 4 organization

- RAM-based FIFO with low fall-through time

- Low-power consumption

Active: 175 mW (typ.)

- Maximum shift frequency 10 MHz

- High data output drive capability

- Asynchronous and simultaneous read and write

- Output Enable pin to enable output data

- High-speed data communications applications

- High-performance CMOS technology

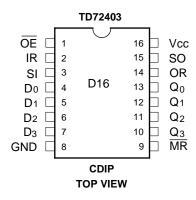

- 16-CERDIP package CDIP2-T16

- Military MIL-PRF-38535, Class level B processing

- Military temperature range (-55°C to +125°C)

A Teledyne Defense Electronics Company

## **Functional Block Diagram**

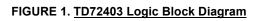

## Part Number Key

## **Pin Configuration**

Note: The case outline is as designated in MIL-STD-1835 and as follows:

| Descriptive designator | Terminals | Package style        |

|------------------------|-----------|----------------------|

| GDIP1-T16              | 16        | Dual-in-line package |

## 1. Scope

1.1 <u>Scope</u>. This drawing describes device requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A.

- 1.2 Lead finish. The lead finish is as specified in MIL-PRF-38535, appendix A.

- 1.3 Absolute maximum ratings.

| Terminal voltage with respect to ground<br>DC output current<br>Storage temperature range<br>Maximum power dissipation (P <sub>D</sub> ) <u>1</u> / | -0.5 V dc to +7.0 V dc<br>50 mA<br>-65°C to +150°C<br>1.0 W |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Lead temperature (soldering, 10 seconds)<br>Thermal resistance, junction-to-case ( $\Theta_{JC}$ )                                                  | +260°C<br>See MIL-STD-1835<br>+175°C                        |

| Junction temperature (T <sub>J</sub> )                                                                                                              | +1/5 C                                                      |

1.4 Recommended operating conditions.

| Supply voltage (V <sub>CC</sub> )<br>Supply voltage (GND)                      | 4.5 V dc to 5.5 V dc<br>0 V dc |

|--------------------------------------------------------------------------------|--------------------------------|

| Input high voltage (SI & SO VIH)                                               | 2.35 V dc minimum              |

| Input high voltage (VIH all others)<br>Input low voltage (SI V <sub>IL</sub> ) |                                |

| Input low voltage (VIL all others)                                             | 0.8 V dc maximum <u>2</u> /    |

| Case operating temperature range (T <sub>C</sub> )                             | -55°C to +125°C                |

$\underline{1}$  Must withstand the added P<sub>D</sub> due to short-circuit, test e.g., I<sub>OS</sub>.

## **2. Electrical Performance**

2.1 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

<sup>2/</sup> -1.5 V undershoots are allowed for 10 ns once per cycle.

## Note: Only Device Types All and 01 shall be applicable.

|                                            | TA               | BLE I. Electrical performance cha                                                                                                                            | aracteristics.       |                |          |             |          |

|--------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|----------|-------------|----------|

| Test                                       | Symbol           | $\begin{array}{c} Conditions \\ -55^{\circ}C \leq T_{C} \leq +125^{\circ}C \\ V_{CC} = 4.5 \ V \ to \ 5.5 \ V \\ unless \ otherwise \ specified \end{array}$ | Group A<br>subgroups | Device<br>type | Lin      | mits<br>Max | Unit     |

| Input low current                          | IIL              | $0 \text{ V} \leq V_{\text{IN}} \leq 5.5 \text{ V}, \text{ V}_{\text{CC}} = 5.5 \text{ V}$                                                                   | 1, 2, 3              | All            | -10      | IViax       | μΑ       |

| Input high current for OE                  | liн              | $0 \text{ V} \leq V_{\text{IN}} \leq 5.5 \text{ V}, \text{ V}_{\text{CC}} = 5.5 \text{ V}$                                                                   | 1, 2, 3              | All            | <u> </u> | +50         | μA       |

| Input high current for all others          | Іін              | $0~V \leq V_{IN} \leq 5.5~V,~V_{CC} = 5.5~V$                                                                                                                 | 1, 2, 3              | All            |          | +10         | μA       |

| Output low voltage                         | Vol              | $V_{CC} = 4.5 \text{ V}, I_{OL} = 8.0 \text{ mA}$<br>$V_{IL} = 0.8 \text{ V}, V_{IH} = 2.0 \text{ V}$                                                        | 1, 2, 3              | All            |          | 0.4         | V        |

| Output high voltage                        | V <sub>OH</sub>  | $V_{CC} = 4.5 \text{ V}, I_{OH} = -4.0 \text{ mA}$ $V_{IL} = 0.8 \text{ V}, V_{IH} = 2.0 \text{ V}$                                                          | 1, 2, 3              | All            | 2.4      |             | V        |

| Output short-circuit<br>current <u>1</u> / | los              | $V_{CC} = 5.5 V, V_0 = 0 V$                                                                                                                                  | 1, 2, 3              | All            | -20      | -110        | mA       |

| Off-state output<br>high current           | Інг              | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = 2.4 V                                                                                                              | 1, 2, 3              | 01-04          |          | +20         | μΑ       |

| Off-state output<br>low current            | ILZ              | V <sub>CC</sub> = 5.5 V, V <sub>O</sub> = 0.4 V                                                                                                              | 1, 2, 3              | 01-04          | -20      |             | μA       |

| Operating supply current                   | lcc              | All inputs = 0.0 V to 3.0 V,<br>$V_{CC}$ = 5.5 V,<br>outputs open, f = 10 MHz                                                                                | 1, 2, 3              | All            |          | 45          | mA       |

| Input capacitance                          | CIN              | $V_{IN} = 0 V, f = 1.0 MHz,$<br>$T_A = +25^{\circ}C, see 4.3.1c$                                                                                             | 4                    | All            |          | 10          | pF       |

| Output capacitance                         | Соит             | $V_{OUT} = 0 V, f = 1.0 MHz,$<br>$T_A = +25^{\circ}C, see 4.3.1c$                                                                                            | 4                    | All            |          | 10          | pF       |

| Functional test                            |                  | See 4.3.1d                                                                                                                                                   | 7, 8A, 8B            | All            |          |             |          |

| Shift in rate                              | fın              | See figures 2 - 8 as                                                                                                                                         | 9, 10, 11            | 01,05          |          | 10          | MHz      |

| ,                                          |                  | applicable <u>2</u> /                                                                                                                                        |                      | 02,06          | <u> </u> | 15          | 1        |

| ,                                          |                  |                                                                                                                                                              |                      | 03,07          | <u> </u> | 25          | 1        |

|                                            | <b>_</b>         | 4                                                                                                                                                            | ļ                    | 04,08          | <b> </b> | 35          | <b>_</b> |

| Shift in to input                          | t <sub>IRL</sub> |                                                                                                                                                              | 9, 10, 11            | 01,05          | ──       | 40          | ns       |

| ready low <u>3</u> /                       |                  |                                                                                                                                                              |                      | 02,06          | ───      | 35          | 4        |

| ,                                          |                  |                                                                                                                                                              |                      | 03,07          | <b> </b> | 21          | 4        |

|                                            |                  | 4                                                                                                                                                            |                      | 04,08          | ───      | 18          | <u> </u> |

| Shift in to input                          | t <sub>IRH</sub> |                                                                                                                                                              | 9, 10, 11            | 01,05          | <b> </b> | 45          | ns       |

| ready high <u>3</u> /                      |                  |                                                                                                                                                              |                      | 02,06          | ───      | 40          | 4        |

| ,                                          |                  |                                                                                                                                                              |                      | 03,07          | ───      | 28          | 4        |

|                                            | +                | 4                                                                                                                                                            | 2 40 44              | 04,08          | ───      | 20          |          |

| Shift out rate                             | fouт             |                                                                                                                                                              | 9, 10, 11            | 01,05          | ──       | 10          | MHz      |

| ,                                          |                  |                                                                                                                                                              |                      | 02,06          | <b> </b> | 15          | -        |

| ,                                          |                  |                                                                                                                                                              |                      | 03,07<br>04,08 | <b> </b> | 25<br>35    | 4        |

See footnotes at end of table.

## Note: Only Device Types All and 01 shall be applicable.

| <b>T</b> .                            |                         | Conditions $-55^{\circ}C \le T_{C} \le +125^{\circ}C$ | 0                    | Davias                |            | .,          |     |

|---------------------------------------|-------------------------|-------------------------------------------------------|----------------------|-----------------------|------------|-------------|-----|

| Test                                  | Symbol                  | $V_{CC}$ = 4.5 V to 5.5 V                             | Group A<br>subgroups | Device<br>type        | Lir<br>Min | nits<br>Max | Uni |

| Chift out to output                   | <b>4</b>                | unless otherwise specified                            | 0 10 11              | 01.05                 | IVIIII     |             |     |

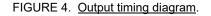

| Shift out to output                   | torl                    | See figures 2 - 8 as                                  | 9, 10, 11            | 01,05                 |            | 40          | ns  |

| ready low <u>3</u> /                  |                         | applicable <u>2</u> /                                 |                      | 02,06<br>03,07        |            | 35<br>19    | -   |

|                                       |                         |                                                       |                      | 03,07                 |            | 18          |     |

| Shift out to output                   | torh                    | -                                                     | 9, 10, 11            | 01,05                 |            | 55          | ns  |

| ready high <u>3</u> /                 | UKH                     |                                                       | 3, 10, 11            | 02,06                 |            | 40          | 113 |

| ready high <u>o</u> ,                 |                         |                                                       |                      | 03,07                 |            | 34          |     |

|                                       |                         |                                                       |                      | 04,08                 |            | 20          |     |

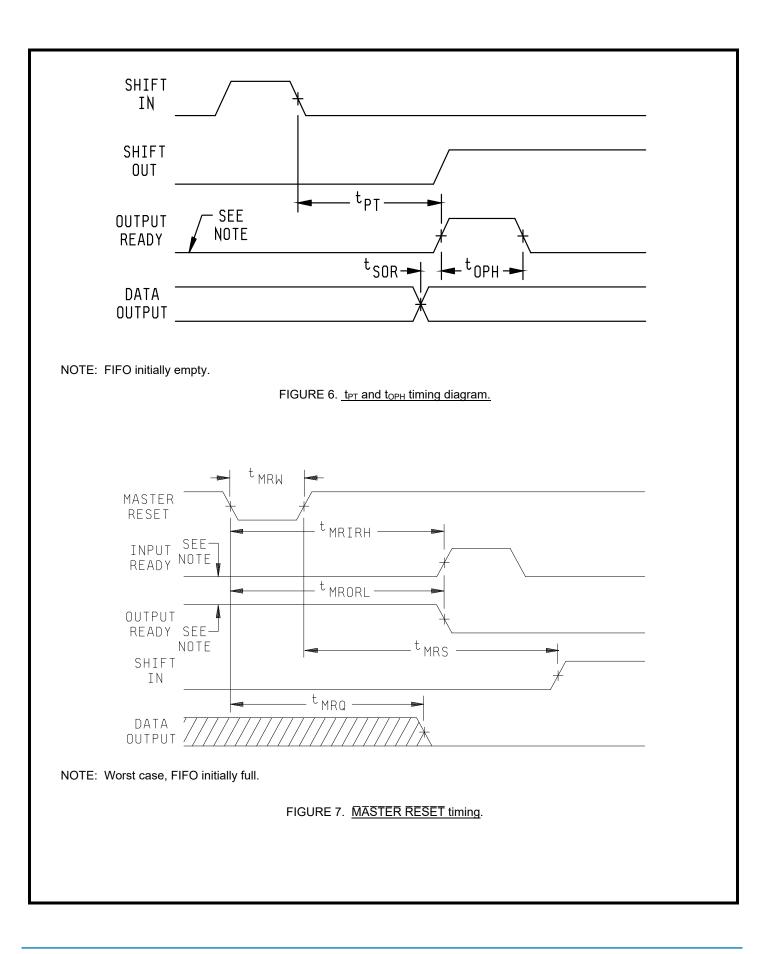

| Output data hold, previous word       | tорн                    | •                                                     | 9, 10, 11            | All                   | 5.0        |             | ns  |

| Output data shift                     | tops                    |                                                       | 9, 10, 11            | 01,02,05,06           |            | 55          | ns  |

| (next word)                           |                         |                                                       |                      | 03,07                 |            | 35          |     |

| ,<br>,                                |                         |                                                       |                      | 04,08                 |            | 25          |     |

| Data throughput<br>or "fall through"  | tрт                     |                                                       | 9, 10, 11            | 01,02,05,06           |            | 65          | ns  |

| 5                                     |                         |                                                       |                      | 03,07                 |            | 40          |     |

|                                       |                         |                                                       |                      | 04,08                 |            | 28          |     |

| MASTERRESET to OR low                 | t <sub>MRORL</sub>      |                                                       | 9, 10, 11            | 01,05                 |            | 40          | ns  |

| -                                     |                         |                                                       |                      | 02,03,06,07           |            | 35          |     |

|                                       |                         |                                                       |                      | 04,08                 |            | 28          |     |

| MASTER RESET to IR high               | t <sub>MRIRH</sub>      |                                                       | 9, 10, 11            | 01,05                 |            | 40          | ns  |

|                                       |                         |                                                       |                      | 02,03,06,07           |            | 35          |     |

|                                       |                         |                                                       |                      | 04,08                 |            | 28          |     |

| MASTER RESET to data                  | <b>t</b> <sub>MRQ</sub> |                                                       | 9, 10, 11            | 01,05                 |            | 40          | ns  |

| output low                            |                         |                                                       |                      | 02,06                 |            | 35          |     |

|                                       |                         |                                                       |                      | 03,07                 |            | 25          |     |

|                                       |                         |                                                       |                      | 04,08                 |            | 20          |     |

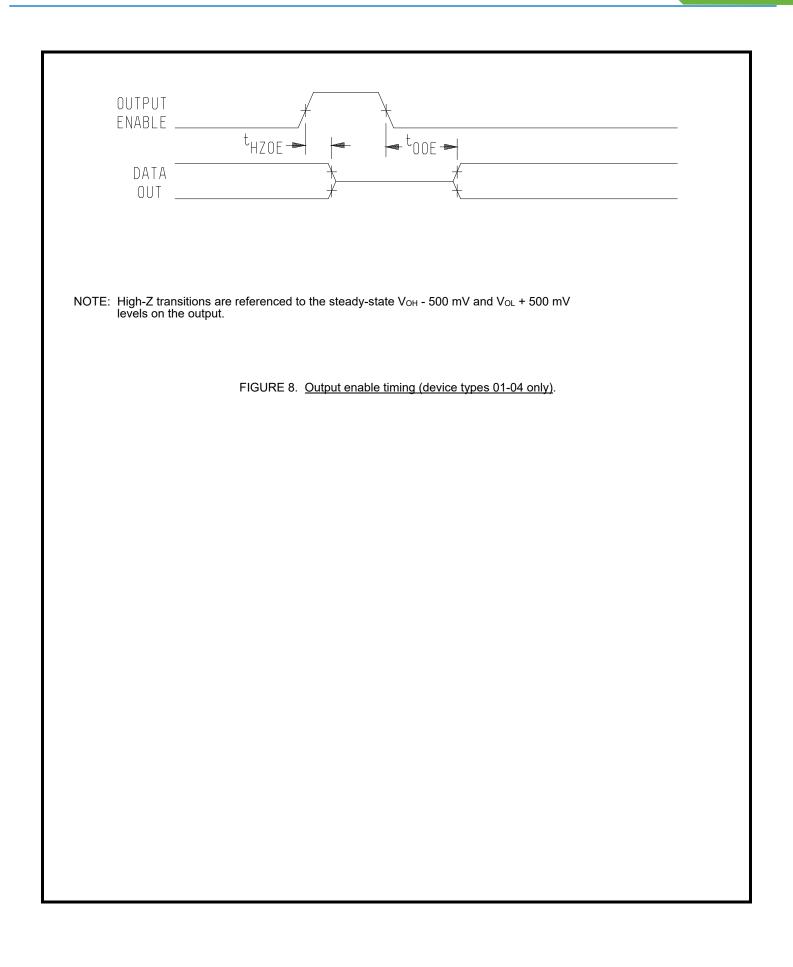

| Output valid from $\overline{OE}$ low | tooe                    |                                                       | 9, 10, 11            | 01                    |            | 35          | ns  |

|                                       |                         |                                                       |                      | 02                    |            | 30          |     |

|                                       |                         |                                                       |                      | 03                    |            | 20          |     |

|                                       |                         |                                                       |                      | 04                    |            | 15          |     |

| Output high impedance                 | t <sub>HZOE</sub>       |                                                       | 9, 10, 11            | 01                    |            | 30          | ns  |

| from OE high 4/                       |                         |                                                       |                      | 02                    |            | 25          |     |

|                                       |                         |                                                       |                      | 03                    |            | 15          |     |

|                                       |                         |                                                       |                      | 04                    |            | 12          |     |

| Input ready pulse<br>high <u>4</u> /  | tiph                    |                                                       | 9, 10, 11            | 01,02,<br>03,05,06,07 | 11         |             | ns  |

| 0 _                                   |                         |                                                       |                      | 04,08                 | 9.0        |             |     |

| Output ready pulse<br>high <u>4</u> / | tорн                    |                                                       | 9, 10, 11            | 01, 02, 03            | 10         |             | ns  |

|                                       |                         |                                                       |                      | 04                    | 5.0        |             | 1   |

## Note: Only Device Types All and 01 shall be applicable.

|                                  |                  | Conditions                                                                                                                                               |                      |                       |        |     | 1    |

|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--------|-----|------|

| Test                             | Symbol           | $\begin{array}{l} \text{Conditions} \\ \text{-55^{\circ}C} \leq T_{C} \leq +125^{\circ}C \\ \text{V}_{CC} = 4.5 \text{ V to } 5.5 \text{ V} \end{array}$ | Group A<br>subgroups | Device<br>type        | Limits |     | Unit |

|                                  |                  | unless otherwise specified                                                                                                                               |                      |                       | Min    | Max |      |

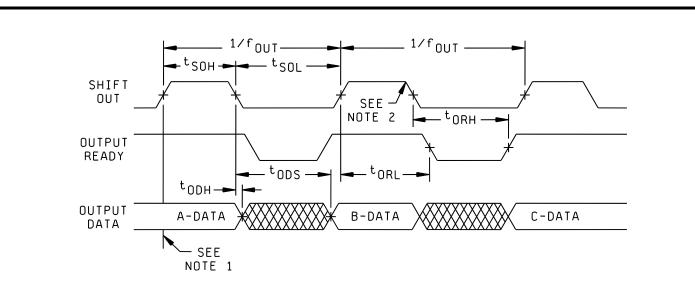

| Shift in high time <u>3</u> /    | tsıн             | See figures 2 - 8 as                                                                                                                                     | 9, 10, 11            | 01,02,05,06           | 11     |     | ns   |

|                                  |                  | applicable <u>2</u> /                                                                                                                                    |                      | 03,07                 | 11     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 9.0    |     |      |

| Shift in low time                | t <sub>SIL</sub> |                                                                                                                                                          | 9, 10, 11            | 01,05                 | 30     |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 02,06                 | 25     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 03,07                 | 24     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 17     |     |      |

| Input data setup time            | tids             |                                                                                                                                                          | 9, 10, 11            | All                   | 0      |     | ns   |

| Input data hold time             | tidh             |                                                                                                                                                          | 9, 10, 11            | 01,05                 | 40     |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 02,06                 | 30     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 03,07                 | 20     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 15     |     |      |

| Shift out high time <u>3</u> /   | tsoн             |                                                                                                                                                          | 9, 10, 11            | 01,02,05,06           | 11     |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 03,07                 | 11     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 9.0    |     |      |

| Shift out low time               | tsol             |                                                                                                                                                          | 9, 10, 11            | 01,02,05,06           | 25     |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 03,07                 | 24     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 17     |     |      |

| MASTER RESET pulse               | t <sub>MRW</sub> |                                                                                                                                                          | 9, 10, 11            | 01,05                 | 30     |     | ns   |

| width                            |                  |                                                                                                                                                          |                      | 02,03,04,06,<br>07,08 | 25     |     |      |

| MASTER RESET pulse to            | t <sub>MRS</sub> |                                                                                                                                                          | 9, 10, 11            | 01,02                 | 35     |     | ns   |

| SI                               |                  |                                                                                                                                                          |                      | 05,06                 | 25     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 03,04,07,08           | 10     |     |      |

| Data setup to IR                 | tsir             |                                                                                                                                                          | 9, 10, 11            | 01,02,03,05,<br>06,07 | 5.0    |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 3.0    |     |      |

| Data hold from IR                | t <sub>HIR</sub> |                                                                                                                                                          | 9, 10, 11            | 01,02,05,06           | 30     |     | ns   |

|                                  |                  |                                                                                                                                                          |                      | 03,07                 | 20     |     |      |

|                                  |                  |                                                                                                                                                          |                      | 04,08                 | 15     |     |      |

| Data setup to OR high <u>4</u> / | tsor             |                                                                                                                                                          | 9, 10, 11            | All                   | 0      |     | ns   |

1/ Not more than one output should be shorted at a time. Duration of the short-circuit condition should not exceed one second. This parameter may not be tested, but shall be guaranteed to the limits specified in table I.

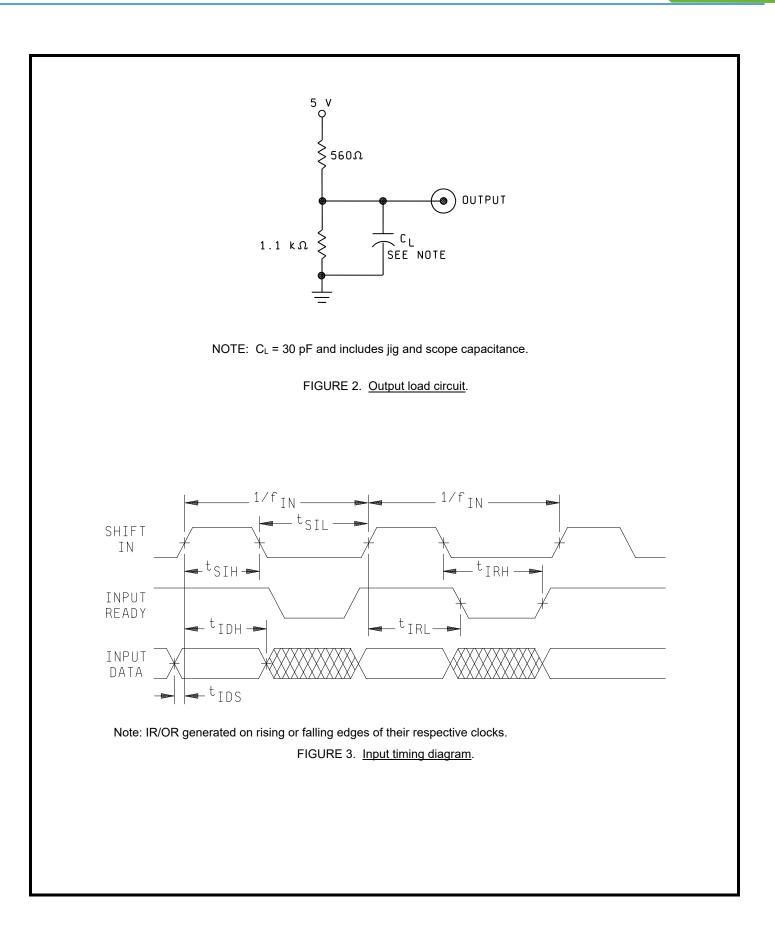

<u>2</u>/ AC measurements assume signal transition times of 5 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 V to 3.0 V and output loading of 30 pF load capacitance. Output timing reference is 1.5 V.

3/ Since these devices are very high speed, care must be exercised in the design of the hardware and timing utilized in the design. Device grounding and decoupling are crucial to correct operation as the device will respond to very small glitches due to long reflective lines, high capacitances or poor supply decoupling and grounding. A monolithic ceramic capacitor of 0.1 µF directly between V<sub>CC</sub> and GND with very short lead lengths is recommended.

4/ May not be tested, but shall be guaranteed to the limits specified in table I.

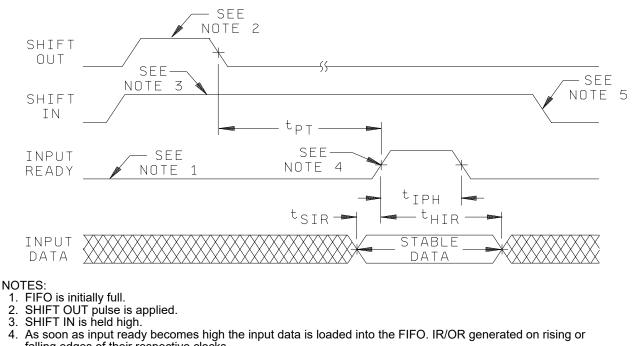

#### NOTES:

- 1. This data is loaded consecutively, A, B, C.

- 2. Data is shifted out when SHIFT OUT makes a high to low transition.

- falling edges of their respective clocks.5. The write pointer is incremented.

FIGURE 5. tIPH, tHIR, and tSIR timing diagram.

## 3. Verification

3.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

3.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition D or E. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- (2)  $_{A} = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

3.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 3.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C<sub>IN</sub> and C<sub>OUT</sub> measurement) shall be measured only for initial qualification and after any process or design changes which may affect input or output capacitance. Capacitance shall be measured between the designated terminal and GND at a frequency of 1 MHz. Sample size is 15 devices with no failures, and all input and output terminals tested.

- d. Subgroups 7 and 8 shall include verification of the device to function correctly.

- 3.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- (2)  $_{A} = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

#### TABLE II. Electrical test requirements.

1/ \* Indicates PDA applies to subgroups 1 and 7.

2/ Any or all subgroups may be combined when using high-speed testers.

- <u>3/</u> \*\* See 4.3.1c.

- <u>4/</u> As a minimum, subgroups 7 and 8 shall consist of verifying the data pattern.

### 4. Packaging

4.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-PRF-38535, appendix A.

### 5. Notes

5.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

5.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractorprepared specification or drawing.

5.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished using DD Form 1692, Engineering Change Proposal.

5.4 <u>Record of users</u>. Military and industrial users shall inform DLA Land and Maritime when a system application requires configuration control and the applicable SMD. DLA Land and Maritime will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DLA Land and Maritime-VA, telephone (614) 692-8108.

5.5 <u>Comments</u>. Comments on this drawing should be directed to DLA Land and Maritime-VA, Columbus, Ohio 43218-3990, or telephone (614) 692-0540.

5.6 <u>Approved sources of supply</u>. Approved sources of supply are listed in MIL-HDBK-103 and QML-38535. The vendors listed in MIL-HDBK-103 and QML-38535 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DLA Land and Maritime-VA.

## Ordering Information

| Order Code   | Description                                         | Package | Shipping Method |

|--------------|-----------------------------------------------------|---------|-----------------|

| TD72403L10DB | First-In/First-Out (FIFO) memory 64 words by 4 bits | 16-CDIP | 28 per Tube     |

## **Revision Information**

| Document             | Description / Date           | Change/Revision Details |  |  |

|----------------------|------------------------------|-------------------------|--|--|

| TD72403-2-2021 Rev 1 | TD72403L10DB / February 2021 | Initial Release         |  |  |

## **Document Categories:**

#### Advance Information

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

#### Preliminary Specification

The data sheet contains preliminary data. Additional data may be added at a later date. Teledyne e2v HiRel Electronics reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### **Product Specification**

The data sheet contains final data. In the event Teledyne e2v HiRel Electronics decides to change the specifications, Teledyne e2v HiRel Electronics will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

## **Sales Contact**

For additional information, Email us at: tdemarketing@teledyne.com ~ www.tdehirel.com

## **Disclaimers**

The information in this document is believed to be reliable. However, Teledyne e2v HiRel Electronics assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Teledyne e2v's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Teledyne e2v product could create a situation in which personal injury or death might occur. Teledyne e2v assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

## **Copyright and Trademark**

Trademarks are the property of their respective owners.

©2021, Teledyne e2v HiRel Electronics. All rights reserved.