October 9, 2007

## QP7216L – CMOS 16 x 16 Multiplier

## **General Description**

The QP7216L is a high-speed, low-power 16 x 16-bit multiplier, ideal for fast, real time digital signal processing applications. Utilization of a modified Booths algorithm and our high-performance, submicron CMOS technology, has achieved speeds comparable to bipolar (20ns max.), at 1/10 the power consumption.

The QP7216L is ideal for applications requiring high-speed multiplication such as fast Fourier transform analysis, digital filtering, graphic display systems, speech synthesis and recognition and in any system requirement where multiplication speeds of a mini/microcomputer are inadequate.

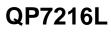

All input registers, as well as LSP and MSP output registers, use the same positive edge-triggered D-type flip-flop. In the QP7216L, there are independent clocks (CLKX, CLKY, CLKM, CLKL) associated with each of these registers.

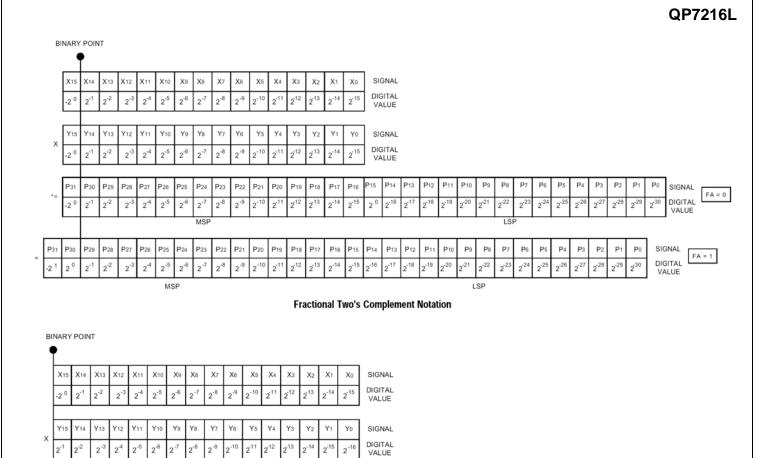

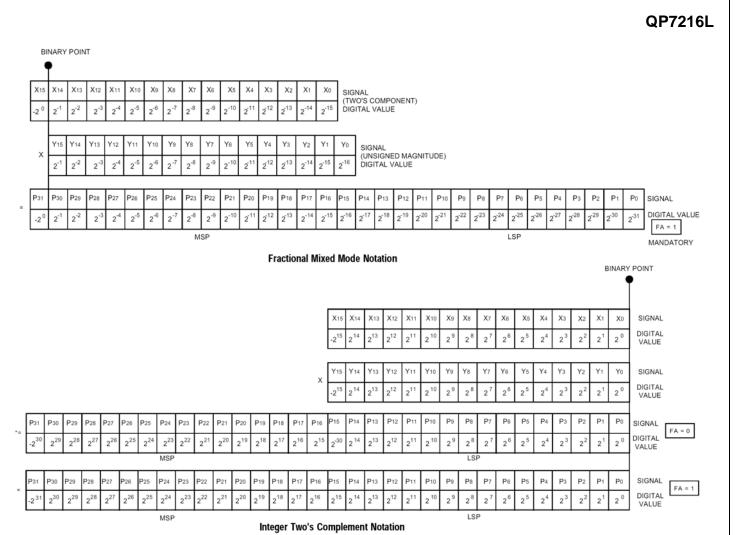

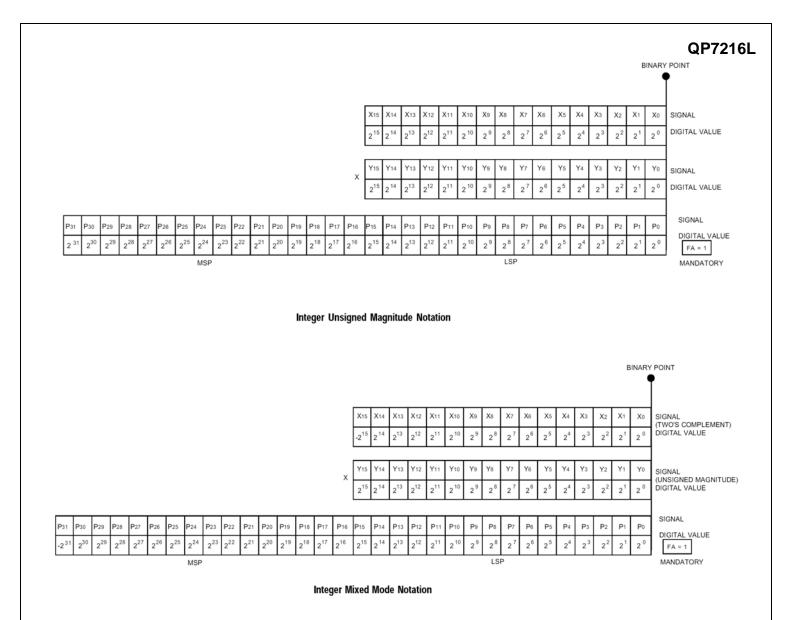

The QP7216L offers additional flexibility with the FA control and MSPSEL<sub>BAR</sub> functions. The FA control formats the output for two's complement by shifting the MSP up one bit and then repeating the sign bit in the MSB of the LSP. MSPSEL<sub>BAR</sub> low selects the MSP to be available at the product output port, while a high selects the LSP to be available. Keeping this pin low will ensure compatibility with the TRW MPY016H.

The QP7216L features:

- 16 x 16 parallel multiplier with double precision product.

- 16ns clocked multiply time

- Low power consumption: 120mA

- Pin and function compatible with TRW MPY016H/K, AMD29516, IDT7216 and CY7C516.

- Tri-state outputs

- Configured for easy array expansion

- User-controlled option for transparent output register mode

- Round control for rounding the MSP

- Input and output directly TTL-compatible

QP Semiconductor products are not authorized for use in any space applications. The inclusion of QP Semiconductor products in space applications implies that the space application manufacturer assumes all risk of such use and in doing so indemnifies QP Semiconductor against all charges.

# **Block Diagram**

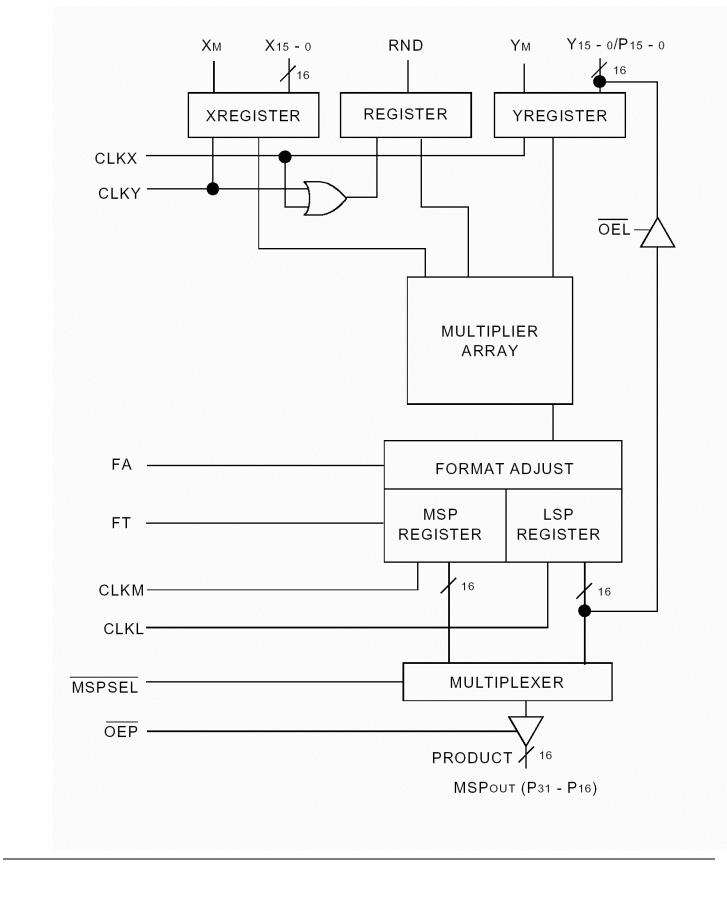

| Pin Name           | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X0-X15             | 1   | Data inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Y0-Y15 /           | I/O | Y0-Y15 are data inputs                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P0-P15             |     | P0-P15 are LSP register output, enabled when OELbar=0                                                                                                                                                                                                                                                                                                                                                                                                       |

| P16-P31            | 0   | Data Output (LSP or MSP)                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OEL <sub>BAR</sub> | I   | Output enable control for LSP (least significant product). When low enables P0-P15. When high P0-P15 high-z (tri-state)                                                                                                                                                                                                                                                                                                                                     |

| OEP <sub>BAR</sub> | I   | Output enable control for MSP (most significant product). When low enables P16-P31. When high P16-P31 high-z (tri-state)                                                                                                                                                                                                                                                                                                                                    |

| XM, YM             | I   | Mode control for each data word. Low designates unsigned data input and high designates two's complement.                                                                                                                                                                                                                                                                                                                                                   |

| RND                |     | "Round" control for rounding of MSP. When high, 1 is added to the most significant bit of LSP. This signal is affected by the state of the FA pin. When FA=1 and RND=1, 1 is added to the 2-15 bit (P15). When RND=1 and FA=0, 1 is added to the 2-16 bit (P14). The RND input is registered. It is clocked on the rising edge of the logical OR of CLKX and CLKY. Rounding always occurs in the positive direction, which may introduce a systematic bias. |

| MSPSELBAR          | 1   | When low, MSP is output on P16-P31. When high, LSP is output on P16-P31.                                                                                                                                                                                                                                                                                                                                                                                    |

| FA                 | 1   | Format adjust control. When high, a full 32-bit product is selected. When low, a left shifted 31-bit product is selected with the sign bit replicated in the LSP. FA is normally high; except for certain fractional two's complement applications (see multiplier input/output formats).                                                                                                                                                                   |

| FT                 | 1   | Flow through control. When high, both MSP and LSP registers are by-passed.                                                                                                                                                                                                                                                                                                                                                                                  |

| CLKX               | 1   | X register clock input. Also clocks RND register.                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLKY               | 1   | Y register clock input. Also clocks RND register.                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLKL               |     | LSP register clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CLKM               | 1   | MSP register clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Absolute Maximum Ratings Stresses above the AMR may cause permanent damage, extended operation at AMR may degrade performance and affect reliability

| Condition                                |                              | Units    | Notes |

|------------------------------------------|------------------------------|----------|-------|

| Power Supply and Input Voltage           | -0.5 to +7.0                 | Volts DC |       |

| Terminal Voltage with respect to GND     | -0.5 to V <sub>CC</sub> +0.5 | Volts    |       |

| DC Output Current                        | 50                           | MA       |       |

| Storage Temperature Range                | -65 to +150                  | °C       |       |

| Lead Temperature (soldering, 10 seconds) | +300                         | °C       |       |

| Junction Temperature (T <sub>J</sub> )   | +150                         | °C       |       |

| Recommended Operating Conditions        |                 |          |            |  |  |  |

|-----------------------------------------|-----------------|----------|------------|--|--|--|

| Condition                               |                 | Units    | Notes      |  |  |  |

|                                         |                 |          |            |  |  |  |

| Supply Voltage Range (V <sub>CC</sub> ) | 4.5 to 5.5      | Volts DC |            |  |  |  |

| Input or Output Voltage Range           | 0.0 to $V_{CC}$ | Volts DC | /5         |  |  |  |

| Minimum High-Level Input Voltage (VIH)  | 2.0             | Volts DC |            |  |  |  |

| Maximum Low-Level Input Voltage (VIL)   | 0.8             | Volts DC |            |  |  |  |

| Maximum high level output current       | -2              | mA       |            |  |  |  |

| Maximum low level output current        | 8               | mA       |            |  |  |  |

| Case Operating Range (T <sub>c</sub> )  | -0C to +70      | °C /5    | Commercial |  |  |  |

| Case Operating Range (T <sub>c</sub> )  | -40C to +85     | °C /5    | Industrial |  |  |  |

| Case Operating Range (T <sub>c</sub> )  | -55 to +125     | °C /5    | Military   |  |  |  |

| _TABLE I – ELECTRICAL PER                         | FORMANC           | CE CHARACTERISTICS                                                          |       |        |              |

|---------------------------------------------------|-------------------|-----------------------------------------------------------------------------|-------|--------|--------------|

| Test                                              | Symbol            | Conditions<br>-55°C ≤TA≤+125°C<br>Unless Otherwise Specified                | Min   | Max    | Unit         |

| _All Devices                                      |                   |                                                                             |       |        |              |

| Input High Voltage                                | VIH               | $V_{CC} = 4.5V$                                                             | 3.0   |        | V            |

| Input Low Voltage                                 | V <sub>IL</sub>   | $V_{CC} = 5.5V$                                                             |       | 0.8    | mA           |

| Input Leakage Current                             | l <sub>LI</sub>   | $V_{CC} = 5.5V, V_{IN} = 0-V_{CC}$                                          | -10.0 | +10.0  | mA           |

| Output Leakage Current                            | I <sub>LO</sub>   | $V_{CC}$ = 5.5V,<br>OE <sub>BAR</sub> =3.5V,<br>V <sub>OUT</sub> = 0 to VCC | -10.0 | +10.0  | μA           |

| Operating Power Supply<br>Current                 | I <sub>CC</sub>   | $V_{CC}$ = 5.5V,<br>OE <sub>BAR</sub> =3.5V,<br>f = 10MHz                   |       | +110.0 | mA           |

| Quiescent Power Supply<br>Current                 | I <sub>CCQ1</sub> | $V_{IN} \ge V_{IH}, V_{IN} \le V_{IL}$                                      |       | +40.0  | mA           |

| Quiescent Power Supply<br>Current                 | I <sub>CCQ2</sub> | $V_{IN} \ge V_{CC} - 0.2V,$<br>$V_{IN} \le 0.2V$                            |       | +25.0  | mA           |

| Increase in Power Supply<br>Current (above 10MHz) | I <sub>CC/f</sub> | $V_{CC} = 5.5V,$<br>$OE_{BAR} = 3.5V$                                       |       | +6.0   | mA/MHz<br>/1 |

| Short Circuit Current /3                          | I <sub>OS</sub>   | $V_{CC} = 5.5V,$<br>$V_{OUT} = 0.0V$                                        |       | -120   | mA           |

| Output High Voltage                               | V <sub>OH</sub>   | V <sub>CC</sub> = 4.5V, I <sub>OH</sub> = -2mA                              | 2.4   |        | V            |

| Output Low Voltage                                | V <sub>OL</sub>   | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 8 mA                              |       | 0.4    | V<br>/2      |

| _TABLE I – ELECTRICAL PER               |                    |                                |     |       | -    |

|-----------------------------------------|--------------------|--------------------------------|-----|-------|------|

| Test                                    | Symbol             | Conditions<br>-55°C ≤TA≤+125°C | Min | Max   | Unit |

|                                         |                    | Unless Otherwise Specified     |     |       |      |

| 20ns                                    |                    |                                |     |       |      |

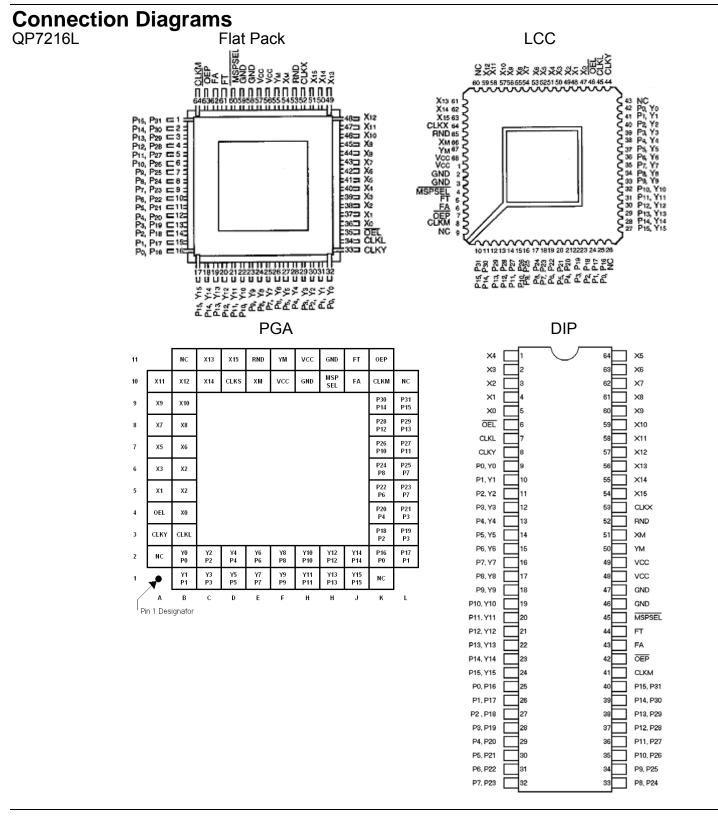

| Unclocked Multiply Time /1              | MUC                | V <sub>CC</sub> = 5.0V         |     | 50 /4 | ns   |

| Clocked Multiply Time                   | MC                 | $V_{CC} = 5.0V$                |     | 20    | ns   |

| X, Y, RND Set-up Time                   | ts                 | $V_{CC} = 5.0V$                | 11  |       | ns   |

| X, Y, RND Hold Time                     | t <sub>H</sub>     | $V_{CC} = 5.0V$                | 1   |       | ns   |

| Clock Pulse Width HIGH                  | t <sub>PWH</sub>   | $V_{CC} = 5.0V$                | 9   |       | ns   |

| Clock Pulse Width LOW                   | t <sub>PWL</sub>   | $V_{CC} = 5.0V$                | 9   |       | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1 | t <sub>PDSEL</sub> | $V_{CC} = 5.0V$                |     | 18    | ns   |

| Output Clock to P /1                    | t <sub>PDP</sub>   | $V_{CC} = 5.0V$                |     | 18    | ns   |

| Output Clock to Y /1                    | t <sub>PDY</sub>   | $V_{CC} = 5.0V$                |     | 18    | ns   |

| Tri-State Enable Time                   | t <sub>ENA</sub>   | V <sub>CC</sub> = 5.0V         |     | 15    | ns   |

| Tri-State Disable Time                  | t <sub>DIS</sub>   | V <sub>CC</sub> = 5.0V         |     | 15    | ns   |

| Clock LOW Hold Time /1                  | t <sub>HCL</sub>   | V <sub>CC</sub> = 5.0V         | 0   |       | ns   |

| CLKX/Y Relative to CLKM/L               |                    |                                |     |       |      |

| _25ns                                   |                    |                                | _   |       |      |

| Unclocked Multiply Time /1              | MUC                | $V_{CC} = 5.0V$                |     | 50 /4 | ns   |

| Clocked Multiply Time                   | MC                 | $V_{CC} = 5.0V$                |     | 25    | ns   |

| X, Y, RND Set-up Time                   | ts                 | $V_{CC} = 5.0V$                | 12  |       | ns   |

| X, Y, RND Hold Time                     | t <sub>H</sub>     | $V_{CC} = 5.0V$                | 2   |       | ns   |

| Clock Pulse Width HIGH                  | t <sub>PWH</sub>   | $V_{CC} = 5.0V$                | 10  |       | ns   |

| Clock Pulse Width LOW                   | t <sub>PWL</sub>   | $V_{CC} = 5.0V$                | 10  |       | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1 | t <sub>PDSEL</sub> | $V_{CC} = 5.0V$                |     | 20    | ns   |

| Output Clock to P /1                    | t <sub>PDP</sub>   | $V_{CC} = 5.0V$                |     | 20    | ns   |

| Output Clock to Y /1                    | t <sub>PDY</sub>   | $V_{CC} = 5.0V$                |     | 20    | ns   |

| Tri-State Enable Time                   | t <sub>ENA</sub>   | $V_{CC} = 5.0V$                |     | 18    | ns   |

| Tri-State Disable Time                  | t <sub>DIS</sub>   | $V_{CC} = 5.0V$                |     | 18    | ns   |

| Clock LOW Hold Time /1                  | t <sub>HCL</sub>   | $V_{CC} = 5.0V$                | 0   |       | ns   |

| CLKX/Y Relative to CLKM/L               |                    |                                |     |       |      |

| _30ns                                   |                    |                                | _   |       | _    |

| Unclocked Multiply Time /1              | MUC                | $V_{CC} = 5.0V$                |     | 50 /4 | ns   |

| Clocked Multiply Time                   | MC                 | $V_{CC} = 5.0V$                |     | 30    | ns   |

| X, Y, RND Set-up Time                   | ts                 | V <sub>CC</sub> = 5.0V         | 12  |       | ns   |

| X, Y, RND Hold Time                     | t <sub>H</sub>     | V <sub>CC</sub> = 5.0V         | 2   |       | ns   |

| Clock Pulse Width HIGH                  | t <sub>₽WH</sub>   | V <sub>CC</sub> = 5.0V         | 10  |       | ns   |

| Clock Pulse Width LOW                   | t <sub>PWL</sub>   | V <sub>CC</sub> = 5.0V         | 10  |       | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1 | t <sub>PDSEL</sub> | V <sub>CC</sub> = 5.0V         |     | 20    | ns   |

| Output Clock to P /1                    | t <sub>PDP</sub>   | V <sub>CC</sub> = 5.0V         |     | 20    | ns   |

| Output Clock to Y /1                    | t <sub>PDY</sub>   | V <sub>CC</sub> = 5.0V         |     | 20    | ns   |

| Tri-State Enable Time                   | t <sub>ENA</sub>   | V <sub>CC</sub> = 5.0V         |     | 20    | ns   |

| Tri-State Disable Time                  | t <sub>DIS</sub>   | V <sub>CC</sub> = 5.0V         |     | 20    | ns   |

| Clock LOW Hold Time /1                  | t <sub>HCL</sub>   | V <sub>CC</sub> = 5.0V         | 0   |       | ns   |

| CLKX/Y Relative to CLKM/L               |                    |                                |     |       |      |

| TABLE I – ELECTRICAL PERI<br>Test                   | Symbol               | Conditions<br>-55°C ≤TA≤+125°C<br>Unless Otherwise Specified | Min | Max | Unit |

|-----------------------------------------------------|----------------------|--------------------------------------------------------------|-----|-----|------|

| 42ns                                                |                      |                                                              |     |     |      |

| Unclocked Multiply Time /1                          | MUC                  | V <sub>CC</sub> = 5.0V                                       |     | 65  | ns   |

| Clocked Multiply Time                               | MC                   | $V_{CC} = 5.0V$                                              |     | 42  | ns   |

| X, Y, RND Set-up Time                               | ts                   | V <sub>CC</sub> = 5.0V                                       | 15  |     | ns   |

| X, Y, RND Hold Time                                 | t <sub>H</sub>       | V <sub>CC</sub> = 5.0V                                       | 3   |     | ns   |

| Clock Pulse Width HIGH                              | t <sub>PWH</sub>     | V <sub>CC</sub> = 5.0V                                       | 15  |     | ns   |

| Clock Pulse Width LOW                               | t <sub>PWL</sub>     | $V_{CC} = 5.0V$                                              | 15  |     | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1             | t <sub>PDSEL</sub>   | $V_{CC} = 5.0V$                                              |     | 25  | ns   |

| Output Clock to P /1                                | t <sub>PDP</sub>     | $V_{CC} = 5.0V$                                              |     | 30  | ns   |

| Output Clock to Y /1                                | t <sub>PDY</sub>     | V <sub>CC</sub> = 5.0V                                       |     | 30  | ns   |

| Tri-State Enable Time                               | t <sub>ENA</sub>     | V <sub>CC</sub> = 5.0V                                       |     | 25  | ns   |

| Tri-State Disable Time                              | t <sub>DIS</sub>     | V <sub>CC</sub> = 5.0V                                       |     | 25  | ns   |

| Clock LOW Hold Time /1                              | t <sub>HCL</sub>     | V <sub>CC</sub> = 5.0V                                       | 0   |     | ns   |

| CLKX/Y Relative to CLKM/L                           |                      |                                                              |     |     |      |

| _55ns                                               |                      |                                                              | _   |     |      |

| Unclocked Multiply Time /1                          | MUC                  | $V_{CC} = 5.0V$                                              |     | 75  | ns   |

| Clocked Multiply Time                               | MC                   | $V_{CC} = 5.0V$                                              |     | 55  | ns   |

| X, Y, RND Set-up Time                               | t <sub>s</sub>       | $V_{CC} = 5.0V$                                              | 20  |     | ns   |

| X, Y, RND Hold Time                                 | t <sub>H</sub>       | $V_{CC} = 5.0V$                                              | 3   |     | ns   |

| Clock Pulse Width HIGH                              | t <sub>PWH</sub>     | $V_{CC} = 5.0V$                                              | 25  |     | ns   |

| Clock Pulse Width LOW                               | t <sub>PWL</sub>     | $V_{CC} = 5.0V$                                              | 25  |     | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1             | t <sub>PDSEL</sub>   | $V_{CC} = 5.0V$                                              |     | 30  | ns   |

| Output Clock to P /1                                | t <sub>PDP</sub>     | $V_{CC} = 5.0V$                                              |     | 30  | ns   |

| Output Clock to Y /1                                | t <sub>PDY</sub>     | $V_{CC} = 5.0V$                                              |     | 30  | ns   |

| Tri-State Enable Time                               | t <sub>ENA</sub>     | $V_{CC} = 5.0V$                                              |     | 31  | ns   |

| Tri-State Disable Time                              | t <sub>DIS</sub>     | $V_{CC} = 5.0V$                                              |     | 30  | ns   |

| Clock LOW Hold Time /1<br>CLKX/Y Relative to CLKM/L | t <sub>HCL</sub>     | $V_{CC} = 5.0V$                                              | 0   |     | ns   |

| 75ns                                                |                      |                                                              |     |     |      |

| Unclocked Multiply Time /1                          | MUC                  | V <sub>CC</sub> = 5.0V                                       |     | 100 | ns   |

| Clocked Multiply Time                               | MC                   | $V_{CC} = 5.0V$                                              |     | 75  | ns   |

| X, Y, RND Set-up Time                               | t <sub>s</sub>       | $V_{CC} = 5.0V$                                              | 25  | 10  | ns   |

| X, Y, RND Hold Time                                 | ts<br>t <sub>H</sub> | $V_{CC} = 5.0V$                                              | 3   |     | ns   |

| Clock Pulse Width HIGH                              | t <sub>PWH</sub>     | $V_{CC} = 5.0V$                                              | 30  |     | ns   |

| Clock Pulse Width LOW                               | t <sub>PWL</sub>     | $V_{CC} = 5.0V$                                              | 30  |     | ns   |

| MSPSEL <sub>BAR</sub> to Product Out /1             |                      | $V_{CC} = 5.0V$                                              |     | 35  | ns   |

| Output Clock to P /1                                |                      | $V_{CC} = 5.0V$                                              |     | 35  | ns   |

| Output Clock to Y /1                                | t <sub>PDP</sub>     | $V_{CC} = 5.0V$                                              |     | 40  | ns   |

| Tri-State Enable Time                               | t <sub>ENA</sub>     | $V_{CC} = 5.0V$                                              |     | 36  | ns   |

| Tri-State Disable Time                              |                      | $V_{CC} = 5.0V$                                              |     | 40  | ns   |

| Clock LOW Hold Time /1<br>CLKX/Y Relative to CLKM/L | t <sub>HCL</sub>     | $V_{\rm CC} = 5.0 V$                                         | 0   |     | ns   |

### /1 – Guaranteed, Not Tested

### /2 - 4mA for $t_{MC} > 65ns$ .

- /3 Duration not to exceed 1 second, one output at a time.

- /4 Unclocked Multiply Time Slower than Original Manufacturer Device

- /5 Maximum PD, Maximum TJ Are Not to Be Exceeded

### TIMING DIAGRAM

2<sup>-18</sup>

In this format an overflow occurs in the attempted multiplication of the two's complement number 1,000...0 with 1,000.0 yeilding an erroneous product of -1 in the fraction case and

Fractional Unsigned Magnitude Notation

2-1

2<sup>-22</sup> 2<sup>-23</sup>

2-20

2-21

2-24

LSP

2-27 2-28

2-30

2<sup>-31</sup>

2-25

2-32

DIGITAL VALUE

FA = 1

MANDATORY

2-26

2<sup>-25</sup>

2<sup>-10</sup>

2-8 2-9

MSP

2<sup>\*12</sup>

2<sup>11</sup>

2<sup>13</sup>

2<sup>-15</sup> 2<sup>-16</sup>

2-14

P31 **P**30 **P**29 P28 P27 P26 P25 P24 P23 P22 P21 **P**20 **P**19 **P**18 P17 **P**16 P15 P14 P13 P12 P11 P10 P9 P8 P7 P6 P5 P4 **P**3 P2 P1 **P**0 SIGNAL

2<sup>-1</sup> 2<sup>-2</sup> 2<sup>-3</sup> 2<sup>-4</sup> 2<sup>-5</sup> 2<sup>-6</sup> 2<sup>-7</sup>

-230 in the integer case.

\* In this format an overflow occurs in the attempted multiplication of the two's complement number 1,000...0 with 1,000.0 yeilding an erroneous product of -1 in the fraction case and -2<sup>30</sup> in the integer case.

| Ordering Information |                 |                    |                        |         |  |  |

|----------------------|-----------------|--------------------|------------------------|---------|--|--|

| Temp Range           | Part Number     | Multiply           | Package (Mil-Std-1835) | Generic |  |  |

|                      |                 | T <sub>Clock</sub> |                        |         |  |  |

| Military             | QP7216L20DB-MIL | 20 ns              | CDIP1-T64              | 7216L   |  |  |

| Military             | QP7216L20LB-MIL | 20 ns              | CQCC1-N68              | 7216L   |  |  |

| Military             | QP7216L20ZB-MIL | 20 ns              | CMGA15-PN 68           | 7216L   |  |  |

| Military             | QP7216L20FB-MIL | 20 ns              | CerQuad 64             | 7216L   |  |  |

| Military             | QP7216L20GB-MIL | 20 ns              | CMGA3-PN 68            | 7216L   |  |  |

| Military             | QP7216L25DB-MIL | 25 ns              | CDIP1-T64              | 7216L   |  |  |

| Military             | QP7216L25LB-MIL | 25 ns              | CQCC1-N68              | 7216L   |  |  |

| Military             | QP7216L25ZB-MIL | 25 ns              | CMGA15-PN 68           | 7216L   |  |  |

| Military             | QP7216L25FB-MIL | 25 ns              | CerQuad 64             | 7216L   |  |  |

| Military             | QP7216L25GB-MIL | 25 ns              | CMGA3-PN 68            | 7216L   |  |  |

| Military             | QP7216L30DB-MIL | 30 ns              | CDIP1-T64              | 7216L   |  |  |

| Military             | QP7216L30LB-MIL | 30 ns              | CQCC1-N68              | 7216L   |  |  |

| Military             | QP7216L30ZB-MIL | 30 ns              | CMGA15-PN 68           | 7216L   |  |  |

| Military             | QP7216L30FB-MIL | 30 ns              | CerQuad 64             | 7216L   |  |  |

| Military             | QP7216L30GB-MIL | 30 ns              | CMGA3-PN 68            | 7216L   |  |  |

| Temp Range | Part Number     | Multiply<br>T <sub>Clock</sub> | Package (Mil-Std-1835) | Generic |

|------------|-----------------|--------------------------------|------------------------|---------|

| Military   | QP7216L42DB-MIL | 42 ns                          | CDIP1-T64              | 7216L   |

| Military   | QP7216L42LB-MIL | 42 ns                          | CQCC1-N68              | 7216L   |

| Military   | QP7216L42ZB-MIL | 42 ns                          | CMGA15-PN 68           | 7216L   |

| Military   | QP7216L42FB-MIL | 42 ns                          | CerQuad 64             | 7216L   |

| Military   | QP7216L42GB-MIL | 42 ns                          | CMGA3-PN 68            | 7216L   |

| Military   | QP7216L55DB-MIL | 55 ns                          | CDIP1-T64              | 7216L   |

| Military   | QP7216L55LB-MIL | 55 ns                          | CQCC1-N68              | 7216L   |

| Military   | QP7216L55ZB-MIL | 55 ns                          | CMGA15-PN 68           | 7216L   |

| Military   | QP7216L55FB-MIL | 55 ns                          | CerQuad 64             | 7216L   |

| Military   | QP7216L55GB-MIL | 55 ns                          | CMGA3-PN 68            | 7216L   |

| Military   | QP7216L75DB-MIL | 75 ns                          | CDIP1-T64              | 7216L   |

| Military   | QP7216L75LB-MIL | 75 ns                          | CQCC1-N68              | 7216L   |

| Military   | QP7216L75ZB-MIL | 75 ns                          | CMGA15-PN 68           | 7216L   |

| Military   | QP7216L75FB-MIL | 75 ns                          | CerQuad 64             | 7216L   |

| Military   | QP7216L75GB-MIL | 75 ns                          | CMGA3-PN 68            | 7216L   |

QP Semiconductor supports Source Control Drawing (SCD), and custom package development for this product family.

### Notes:

Package outline information and specifications are defined by Mil-Std-1835 package dimension requirements.

"-MIL" products manufactured by QP Semiconductor are compliant to the assembly, burn-in, test and quality conformance requirements of Test Methods 5004 & 5005 of Mil-Std-883 for Class B devices. This datasheet defines the electrical test requirements for the device(s).

The listed drawings, Mil-PRF-38535, Mil-Std-883 and Mil-Std-1835 are available online at http://www.dscc.dla.mil/

Additional information is available at our website http://www.qpsemi.com