National Semiconductor

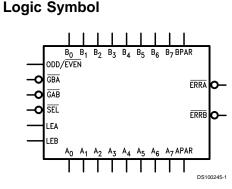

# 54ACT899 9-Bit Latchable Transceiver with Parity Generator/Checker

### **General Description**

The ACT899 is a 9-bit to 9-bit parity transceiver with transparent latches. The device can operate as a feed-through transceiver or it can generate/check parity from the 8-bit data busses in either direction. The ACT899 features independent latch enables for the A-to-B direction and the B-to-A direction, a select pin for ODD/EVEN parity, and separate error signal output pins for checking parity.

#### Features

- Latchable transceiver with output sink of 24 mA

- Option to select generate parity and check or

- "feed-through" data/parity in directions A-to-B or B-to-A

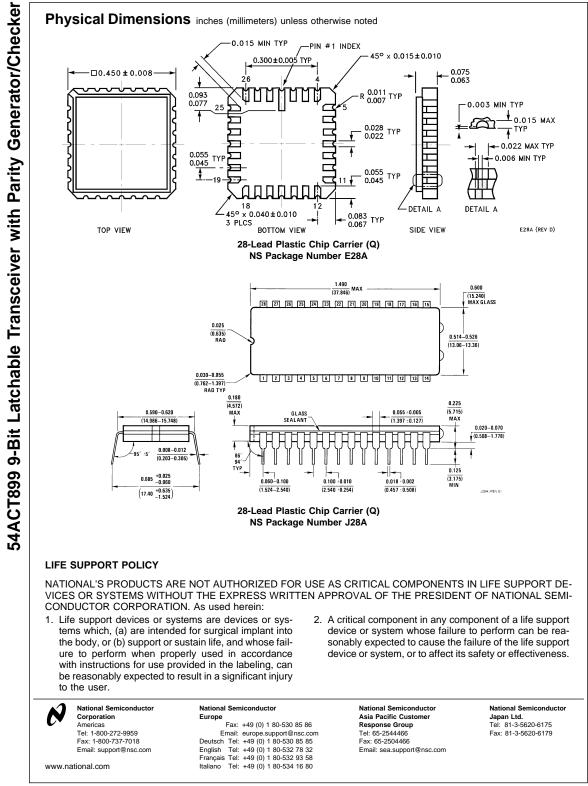

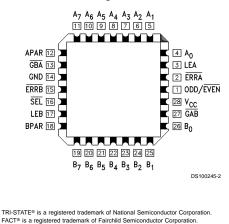

## **Connection Diagram**

### Pin Assignment for LCC

- Independent latch enable for A-to-B and B-to-A directions

- Select pin for ODD/EVEN parity

- ERRA and ERRB output pins for parity checking

- Ability to simultaneously generate and check parity

- May be used in system applications in place of the '280

- May be used in system applications in place of the '657 and '373 (no need to change T/R to check parity)

- 4 kV minimum ESD immunity

- Standard Microcircuit Drawing (SMD) 5962-9314101

| Pin Names                      | Description                                                                           |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| A <sub>0</sub> -A <sub>7</sub> | A Bus Data Inputs/Data Outputs                                                        |  |  |  |

| B <sub>0</sub> -B <sub>7</sub> | B Bus Data Inputs/Data Outputs                                                        |  |  |  |

| APAR, BPAR                     | A and B Bus Parity Inputs                                                             |  |  |  |

| ODD/EVEN                       | ODD/EVEN Parity Select, Active LOW for EVEN Parity                                    |  |  |  |

| GBA, GAB                       | Output Enables for A or B Bus, Active LOW                                             |  |  |  |

| SEL                            | Select Pin for Feed-Through or<br>Generate Mode, LOW for Generate<br>Mode             |  |  |  |

| LEA, LEB                       | Latch Enables for A and B Latches,<br>HIGH for Transparent Mode                       |  |  |  |

| ERRA, ERRB                     | Error Signals for Checking Generated<br>Parity with Parity In, LOW if Error<br>Occurs |  |  |  |

54ACT899 9-Bit Latchable Transceiver with Parity Generator/Checker

© 1998 National Semiconductor Corporation DS100245

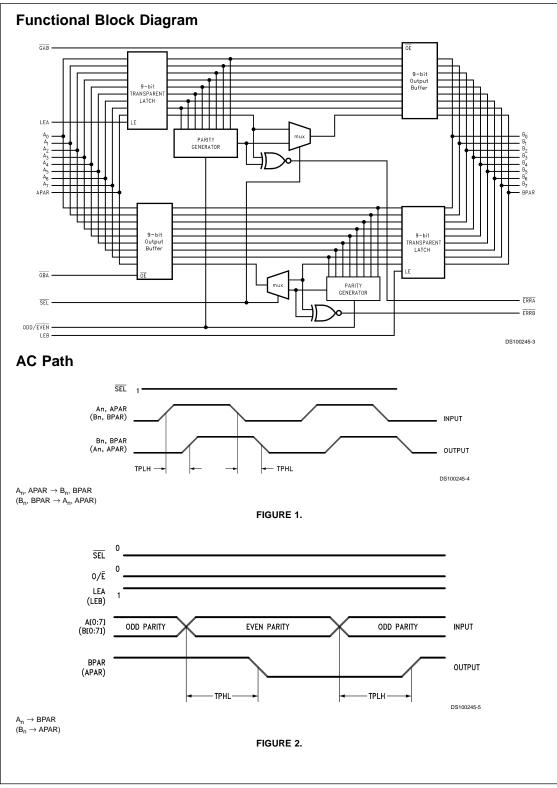

### **Functional Description**

The ACT899 has three principal modes of operation which are outlined below. These modes apply to both the A-to-B and B-to-A directions.

Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEB (LEA) is HIGH and the Mode Select (SEL) is LOW, the parity generated from B[0:7] (A[0:7]) can be checked and monitored by ERRB (ERRA).

# Bus A (B) communicates to Bus B (A) in a feed-through mode if <u>SEL</u> is <u>HIGH</u>. Parity is still generated and checked as <u>ERRA</u> and <u>ERRB</u> in the feed-through mode (can be used as an interrupt to signal a data/parity bit error to the CPU). Independent Latch Enables (LEA and LEB) allow other permutations of generating/checking (see Function Table

below).

### **Function Table**

| Inputs |                    |   | Operation |   |                                                                                                                                                                                                                                                                    |  |  |  |  |

|--------|--------------------|---|-----------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GAB    | AB GBA SEL LEA LEB |   |           |   | 1                                                                                                                                                                                                                                                                  |  |  |  |  |

| Н      | Н                  | Х | Х         | Х | Busses A and B are TRI-STATE®.                                                                                                                                                                                                                                     |  |  |  |  |

| Н      | L                  | L | L         | Н | Generates parity from B[0:7] based on O/ $\overline{E}$ (Note 1). Generated p $\rightarrow$ APAR. Generated parity checked against BPAR and output as $\overline{ERRB}$ .                                                                                          |  |  |  |  |

| Н      | L                  | L | Н         | Н | Generates parity from B[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ APAR. Generated parity checked against BPAR and output as $\overline{ERRB}$ . Generated parity also fed back through the A latch for generate/check as $\overline{ERRA}$ . |  |  |  |  |

| Н      | L                  | L | Х         | L | Generates parity from B latch data based on O/Ē. Generated parity →<br>APAR. Generated parity checked against latched BPAR and output as<br>ERRB.                                                                                                                  |  |  |  |  |

| Н      | L                  | н | Х         | н | $BPAR/B[0:7] \rightarrow APAR/A0:7]$ Feed-through mode. Generated particle checked against BPAR and output as ERRB.                                                                                                                                                |  |  |  |  |

| Н      | L                  | н | н         | н | $BPAR/B[0:7] \to APAR/A[0:7]$                                                                                                                                                                                                                                      |  |  |  |  |

|        |                    |   |           |   | Feed-through mode. Generated parity checked against BPAR and output as ERRB. Generated parity also fed back through the A latch for generate/check as ERRA.                                                                                                        |  |  |  |  |

| L      | н                  | L | Н         | L | Generates parity for A[0:7] based on O/ $\overline{E}$ . Generated parity $\rightarrow$ BP/ Generated parity checked against APAR and output as $\overline{ERRA}$ .                                                                                                |  |  |  |  |

| L      | н                  | L | Н         | Н | Generates parity from A[0:7] based on $O/\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against APAR and output as ERRA. Generated parity also fed back through the B latch for generate/check as ERRB.                             |  |  |  |  |

| L      | н                  | L | L         | Х | Generates parity from A latch data based on $O/\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against latched APAR and output as ERRA.                                                                                              |  |  |  |  |

| L      | н                  | н | н         | L | $APAR/A[0:7] \rightarrow BPAR/B[0:7]$                                                                                                                                                                                                                              |  |  |  |  |

|        |                    |   |           |   | Feed-through mode. Generated parity checked against APAR and output as ERRA.                                                                                                                                                                                       |  |  |  |  |

| L      | н                  | н | н         | н | $APAR/A[0:7] \rightarrow BPAR/B[0:7]$                                                                                                                                                                                                                              |  |  |  |  |

|        |                    |   |           |   | Feed-through mode. Generated parity checked against APAR and output as ERRA. Generated parity also fed back through the B latch for generate/check as ERRB.                                                                                                        |  |  |  |  |

H = HIGH Voltage Level L = LOW Voltage Level

X = Immaterial

Note 1: O/E = ODD/EVEN

3

4

### Absolute Maximum Ratings (Note 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )                     | -0.5V to +7.0V                  |

|-------------------------------------------------------|---------------------------------|

| DC Input Diode Current (IIK)                          |                                 |

| $V_1 = -0.5V$                                         | –20 mA                          |

| $V_{1} = V_{CC} + 0.5V$                               | +20 mA                          |

| DC Input Voltage (V <sub>I</sub> )                    | –0.5V to V <sub>CC</sub> + 0.5V |

| DC Output Diode Current (I <sub>OK</sub> )            |                                 |

| $V_{O} = -0.5V$                                       | –20 mA                          |

| $V_{O} = V_{CC} + 0.5V$                               | +20 mA                          |

| DC Output Voltage (V <sub>O</sub> )                   | –0.5V to V <sub>CC</sub> + 0.5V |

| DC Output Source                                      |                                 |

| or Sink Current (I <sub>O</sub> )                     | ±50 mA                          |

| DC V <sub>CC</sub> or Ground Current                  |                                 |

| per Output Pin (I <sub>CC</sub> or I <sub>GND</sub> ) | ±50 mA                          |

| Storage Temperature (T <sub>STG</sub> )               | -65°C to +150°C                 |

|                                                       |                                 |

| DC Latch-Up Source or<br>Sink Current<br>Junction Temperature (T <sub>J</sub> )<br>CDIP | ±300 mA<br>175°C |

|-----------------------------------------------------------------------------------------|------------------|

| Recommended Operating<br>Conditions                                                     |                  |

| Supply Voltage (V <sub>CC</sub> )<br>'ACT                                               | 4.5V to 5.5V     |

| AUT                                                                                                                                                      | 4.57 10 5.57    |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Input Voltage (V <sub>I</sub> )                                                                                                                          | 0V to $V_{CC}$  |  |  |  |  |

| Output Voltage (V <sub>O</sub> )                                                                                                                         | 0V to $V_{CC}$  |  |  |  |  |

| Operating Temperature (T <sub>A</sub> )                                                                                                                  |                 |  |  |  |  |

| 54ACT                                                                                                                                                    | –55°C to +125°C |  |  |  |  |

| Minimum Input Edge Rate $\Delta V/\Delta t$                                                                                                              |                 |  |  |  |  |

| 'ACT Devices                                                                                                                                             |                 |  |  |  |  |

| V <sub>IN</sub> from 0.8V to 2.0V                                                                                                                        |                 |  |  |  |  |

| V <sub>CC</sub> @ 4.5V, 5.5V                                                                                                                             | 125 mV/ns       |  |  |  |  |

| <b>Note 2:</b> Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without |                 |  |  |  |  |

to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. National does not recommend operation of FACT® circuits outside databook specifications. **Note 3:** PLCC packaging is not recommended for applications requiring greater than 2000 temperature cycles from -40°C to +125°C.

## DC Electrical Characteristics for 'ACT Family Devices

|                  |                                |                 | 54ACT                |       |                                      |

|------------------|--------------------------------|-----------------|----------------------|-------|--------------------------------------|

| Symbol           | Parameter                      | V <sub>cc</sub> | T <sub>A</sub> =     | Units | Conditions                           |

|                  |                                | (V)             | –55°C to +125°C      |       |                                      |

|                  |                                |                 | Guaranteed<br>Limits |       |                                      |

| V <sub>IH</sub>  | Minimum High Level             | 4.5             | 2.0                  | V     | V <sub>OUT</sub> = 0.1V              |

|                  | Input Voltage                  | 5.5             | 2.0                  |       | or $V_{CC} - 0.1V$                   |

| V <sub>IL</sub>  | Maximum Low Level              | 4.5             | 0.8                  | V     | V <sub>OUT</sub> = 0.1V              |

|                  | Input Voltage                  | 5.5             | 0.8                  |       | or $V_{CC} - 0.1V$                   |

| V <sub>он</sub>  | Minimum High Level             | 4.5             | 4.4                  | V     | I <sub>OUT</sub> = -50 μA            |

|                  | Output Voltage                 | 5.5             | 5.4                  |       |                                      |

|                  |                                |                 |                      |       | (Note 4)                             |

|                  |                                |                 |                      |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

|                  |                                | 4.5             | 3.70                 | V     | I <sub>ОН</sub> = -24 mA             |

|                  |                                | 5.5             | 4.70                 |       | I <sub>ОН</sub> = -24 mA             |

| V <sub>OL</sub>  | Maximum Low Level              | 4.5             | 0.1                  | V     | I <sub>OUT</sub> = 50 μA             |

|                  | Output Voltage                 | 5.5             | 0.1                  |       |                                      |

|                  |                                |                 |                      |       | (Note 4)                             |

|                  |                                |                 |                      |       | $V_{IN} = V_{IL} \text{ or } V_{IH}$ |

|                  |                                | 4.5             | 0.50                 | V     | I <sub>OL</sub> = 24 mA              |

|                  |                                | 5.5             | 0.50                 |       | I <sub>OL</sub> = 24 mA              |

| I <sub>IN</sub>  | Maximum Input                  | 5.5             | ±1.0                 | μA    | $V_{I} = V_{CC}, GND$                |

|                  | Leakage Current                |                 |                      |       |                                      |

| l <sub>oz</sub>  | Maximum TRI-STATE              | 5.5             | ±10.0                | μA    | $V_{I} = V_{IL}, V_{IH}$             |

|                  | Leakage Current                |                 |                      |       | $V_{O} = V_{CC}, GND$                |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input | 5.5             | 1.6                  | mA    | $V_1 = V_{CC} - 2.1V$                |

| I <sub>OLD</sub> | Minimum Dynamic                | 5.5             | 50                   | mA    | V <sub>OLD</sub> = 1.65V Max         |

| I <sub>OHD</sub> | Output Current (Note 5)        | 5.5             | -50                  | mA    | V <sub>OHD</sub> = 3.85V Min         |

|                                       |                                                                                                                                               |                     | 54AC                                    | т     |                     |                                                      |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|-------|---------------------|------------------------------------------------------|

| Symbol                                | Parameter                                                                                                                                     | V <sub>cc</sub>     | T <sub>A</sub> =                        |       | Units               | Conditions                                           |

|                                       |                                                                                                                                               | (V)                 | -55°C to +125°C<br>Guaranteed<br>Limits |       |                     |                                                      |

|                                       |                                                                                                                                               |                     |                                         |       |                     |                                                      |

|                                       |                                                                                                                                               |                     |                                         |       |                     |                                                      |

| I <sub>CC</sub>                       | Maximum Quiescent<br>Supply Current                                                                                                           | 5.5                 | 160.0                                   | )     | μA                  | V <sub>IN</sub> = V <sub>CC</sub><br>or GND (Note 6) |

| Note 5: Ma<br>Note 6: I <sub>CC</sub> | kimum of 9 outputs loaded; thresholds on inpu<br>kimum test duration 2.0 ms, one output loadec<br>for 54ACT @ 25°C is identical to 74ACT @ 25 | l at a time.<br>°C. |                                         |       |                     |                                                      |

|                                       |                                                                                                                                               | , <b>5</b><br>      | 54                                      | ACT   |                     | 1                                                    |

|                                       |                                                                                                                                               | V <sub>cc</sub>     |                                         | –55°C | $\neg$              | Fig.                                                 |

| Symbol                                | Parameter                                                                                                                                     | (V)                 |                                         | 125°C | Units               | No.                                                  |

| ,                                     |                                                                                                                                               | (Note 7)            | $C_{L} = 50 \text{ pF}$                 |       |                     |                                                      |

|                                       |                                                                                                                                               |                     | Min                                     | Max   |                     |                                                      |

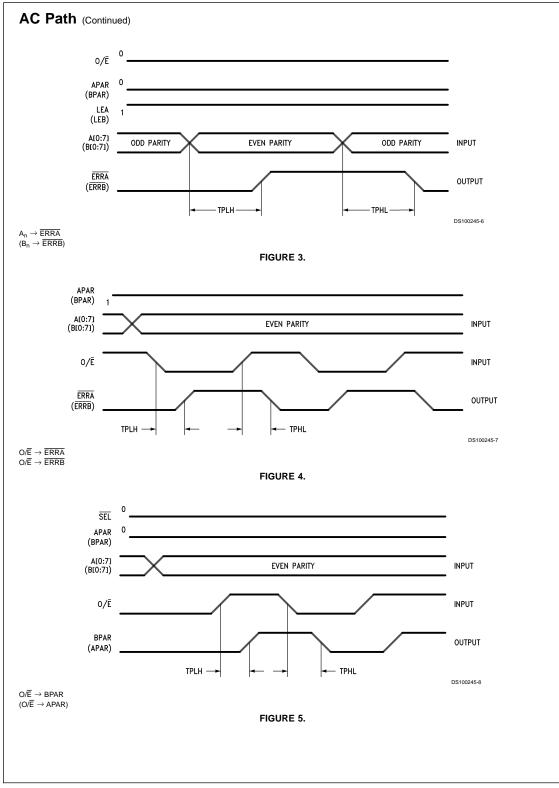

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 13.5  | ns                  | Figure 1                                             |

| PHL                                   | A <sub>n</sub> , B <sub>n</sub> to B <sub>n</sub> , A <sub>n</sub>                                                                            |                     |                                         |       |                     |                                                      |

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 11.0  | ns                  | Figure 1                                             |

| PHL                                   | APAR, BPAR to BPAR, APAR                                                                                                                      |                     |                                         |       |                     |                                                      |

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 16.0  | ns                  | Figure 2                                             |

| PHL                                   | A <sub>n</sub> , B <sub>n</sub> to BPAR, APAR                                                                                                 |                     |                                         |       | <b>F</b> i <b>o</b> |                                                      |

| <sup>I</sup> PLH                      | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 16.0  | ns                  | Figure 3                                             |

| PHL                                   | A <sub>n</sub> , B <sub>n</sub> to ERRA, ERRB                                                                                                 | 5.0                 | 1 5                                     | 16.0  |                     | Eiguro 4                                             |

| PLH                                   | Propagation Delay<br>ODD/EVEN to ERRA, ERRB                                                                                                   | 5.0                 | 1.5                                     | 16.0  | ns                  | Figure 4                                             |

|                                       | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 14.5  | ns                  | Figure 5                                             |

| PHL                                   | ODD/EVEN to APAR, BPAR                                                                                                                        |                     |                                         |       |                     |                                                      |

|                                       | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 11.5  | ns                  | Figure 6                                             |

| PHL                                   | APAR, BPAR to ERRA, ERRB                                                                                                                      |                     |                                         |       |                     |                                                      |

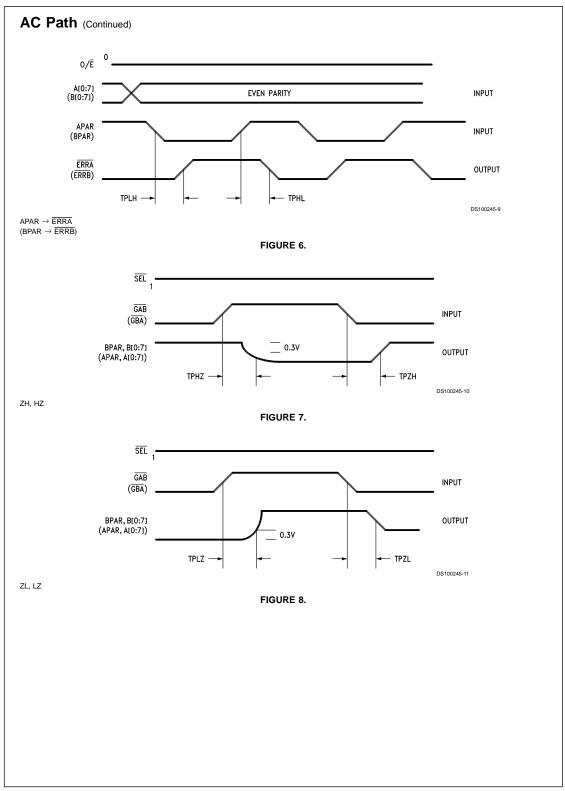

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 12.5  | ns                  | Figure 9                                             |

| PHL                                   | SEL to APAR, BPAR                                                                                                                             |                     |                                         |       |                     |                                                      |

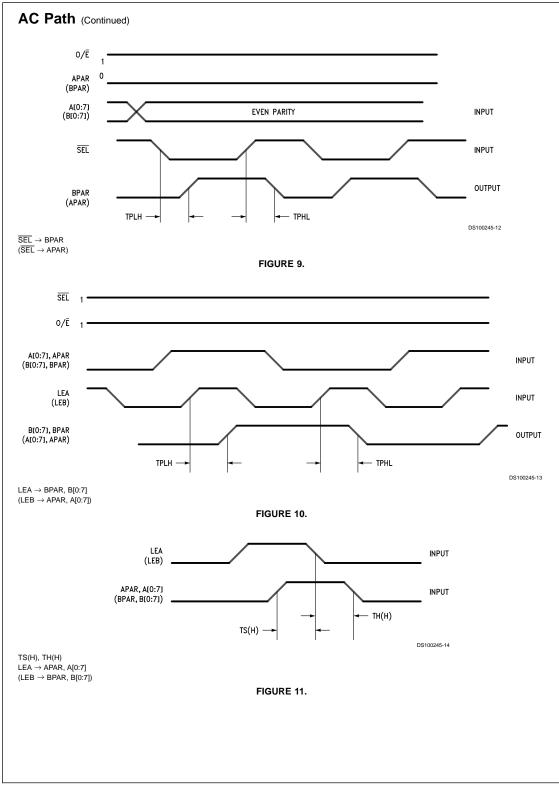

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 13.5  | ns                  | Figures 10, 11                                       |

| PHL                                   | LEB to A <sub>n</sub> , B <sub>n</sub>                                                                                                        |                     |                                         |       |                     |                                                      |

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 16.0  | ns                  | Figures 10, 11                                       |

| PHL                                   | LEA to APAR, BPAR                                                                                                                             |                     |                                         |       |                     |                                                      |

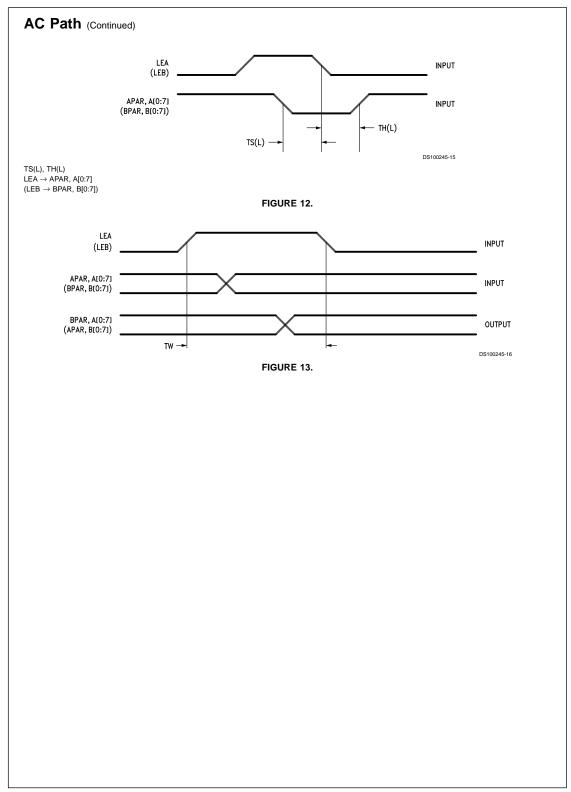

| PLH                                   | Propagation Delay                                                                                                                             | 5.0                 | 1.5                                     | 16.0  | ns                  | Figure 12                                            |

| PHL                                   | LEA, LEB to ERRA, ERRB                                                                                                                        |                     | 4 -                                     | 40.0  |                     |                                                      |

| PZH                                   | Output Enable Time                                                                                                                            | 5.0                 | 1.5                                     | 16.0  | ns                  | Figures 7, 8                                         |

| PZL                                   | GBA or GAB to A <sub>n</sub> , B <sub>n</sub><br>Output Enable Time                                                                           | <b>F</b> 0          | 4 5                                     | 44.0  |                     | Figure 7.0                                           |

| PZH                                   | $\overline{\text{GBA}}$ or $\overline{\text{GAB}}$ to BPAR or APAR                                                                            | 5.0                 | 1.5                                     | 11.0  | ns                  | Figures 7, 8                                         |

| PZL                                   | Output Disable Time                                                                                                                           | 5.0                 | 1.5                                     | 11.0  |                     | Figures 7, 8                                         |

| PHZ                                   | $\overline{\text{GBA}}$ or $\overline{\text{GAB}}$ to $A_n$ , $B_n$                                                                           | 5.0                 | 1.0                                     | 11.0  | ns                  | riguies 7, 8                                         |

| PHL                                   | ODA OF GAD TO An, Dn                                                                                                                          |                     |                                         |       | 1                   |                                                      |

| PHZ                                   | Output Disable Time                                                                                                                           | 5.0                 | 1.5                                     | 11.0  | ns                  | Figures 7, 8                                         |

### AC Operating Requirements

| Symbol         | Parameter                                                                    | V <sub>cc</sub><br>(V)<br>(Note 8) | $54ACT$ $T_A = -55°C$ to +125°C $C_L = 50 \text{ pF}$ Guaranteed Minimum | Units | Fig.<br>No.       |

|----------------|------------------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------|-------|-------------------|

| t <sub>s</sub> | Setup Time, HIGH or LOW<br>A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB | 5.0                                | 3.0                                                                      | ns    | Figures<br>11, 12 |

| t <sub>h</sub> | Hold Time, HIGH or LOW<br>A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB  | 5.0                                | 3.0                                                                      | ns    | Figures<br>11, 12 |

| t <sub>w</sub> | Pulse Width for LEB, LEA                                                     | 5.0                                | 4.0                                                                      | ns    | Figure 13         |

**Note 8:** Voltage Range 5.0 = 5.0V ±0.5V.

## Capacitance

| Symbol          | Parameter         | Тур | Units | Conditions      |

|-----------------|-------------------|-----|-------|-----------------|

| C <sub>IN</sub> | Input Capacitance | 4.5 | pF    | $V_{CC} = 5.0V$ |

| C <sub>PD</sub> | Power Dissipation | 210 | pF    | $V_{CC} = 5.0V$ |

|                 | Capacitance       |     |       |                 |