July 1998

54ABT240 Octal Buffer/Line Driver with TRI-STATE Outputs

# National Semiconductor

## 54ABT240 Octal Buffer/Line Driver with TRI-STATE® Outputs

#### **General Description**

The 'ABT240 is an inverting octal buffer and line driver designed to be employed as a memory address driver, clock driver and bus oriented transmitter or receiver which provides improved PC board density.

- Guaranteed latchup protection

- High impedance glitch free bus loading during entire power up and power down cycle

- Nondestructive hot insertion capability

- Standard Microcircuit Drawing (SMD) 5962-9318801

#### Features

Output sink capability of 48 mA, source capability of 24 mA

#### **Ordering Code**

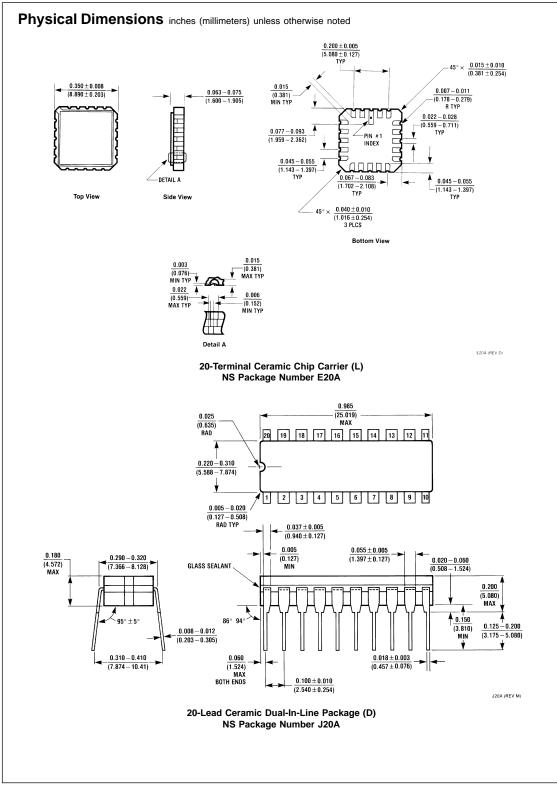

| Military      | Package<br>Number | Package Description                           |

|---------------|-------------------|-----------------------------------------------|

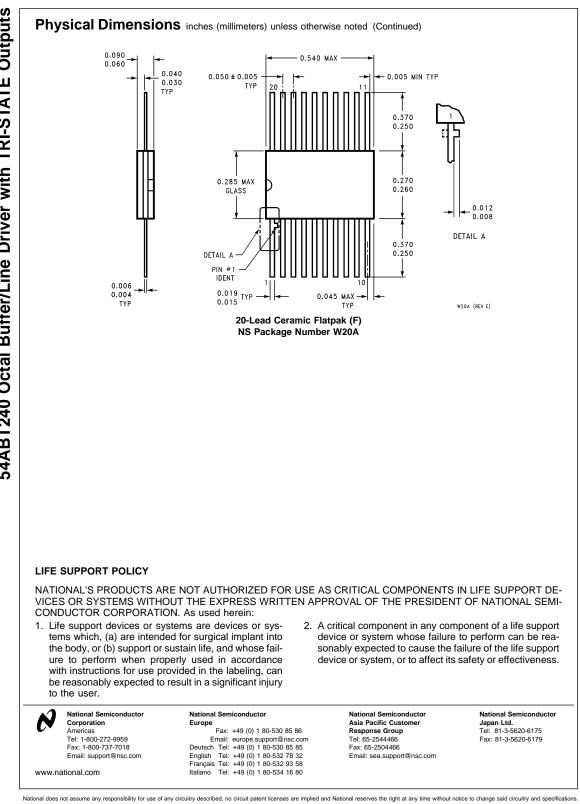

| 54ABT240J-QML | J20A              | 20-Lead Ceramic Dual-In-Line                  |

| 54ABT240W-QML | W20A              | 20-Lead Cerpack                               |

| 54ABT240E-QML | E20A              | 20-Lead Ceramic Leadless Chip Carrier, Type C |

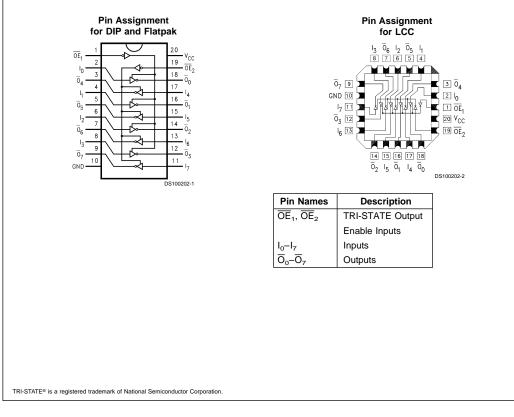

## **Connection Diagrams**

## **Truth Tables**

| Inp                    | uts                   | Outputs                      |  |  |

|------------------------|-----------------------|------------------------------|--|--|

| OE <sub>1</sub>        | l <sub>n</sub>        | (Pins 12, 14, 16, 18)        |  |  |

| L                      | L                     | Н                            |  |  |

| L                      | Н                     | L                            |  |  |

| н                      | х                     | Z                            |  |  |

|                        |                       |                              |  |  |

| Inp                    | uts                   | Outputs                      |  |  |

| Inp<br>OE <sub>2</sub> | uts<br>I <sub>n</sub> | Outputs<br>(Pins 3, 5, 7, 9) |  |  |

| · · ·                  |                       | -                            |  |  |

| · ·                    |                       | (Pins 3, 5, 7, 9)            |  |  |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Z = High Impedance

## Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

| Storage Temperature              | –65°C to +150°C       |

|----------------------------------|-----------------------|

| Ambient Temperature under Bias   | -55°C to +125°C       |

| Junction Temperature under Bias  |                       |

| Ceramic                          | –55°C to +175°C       |

| V <sub>CC</sub> Pin Potential to |                       |

| Ground Pin                       | -0.5V to +7.0V        |

| Input Voltage (Note 2)           | -0.5V to +7.0V        |

| Input Current (Note 2)           | -30 mA to +5.0 mA     |

| Voltage Applied to Any Output    |                       |

| in the Disabled or               |                       |

| Power-Off State                  | -0.5V to 5.5V         |

| in the HIGH State                | –0.5V to $V_{\rm CC}$ |

| Current Applied to Output<br>in LOW State (Max)<br>DC Latchup Source Current<br>(Across Comm Operating<br>Range) | twice the rated $I_{OL}$ (mA) –150 mA |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Over Voltage Latchup (I/O)                                                                                       | 10V                                   |

| Recommended Ope<br>Conditions                                                                                    | rating                                |

| Free Air Ambient Temperature<br>Military                                                                         | -55°C to +125°C                       |

| Supply Voltage                                                                                                   |                                       |

| Military                                                                                                         | +4.5V to +5.5V                        |

| Minimum Input Edge Rate                                                                                          | $(\Delta V/\Delta t)$                 |

| Data Input                                                                                                       |                                       |

**Note 1:** Absolute maximum ratings are values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Either voltage limit or current limit is sufficient to protect inputs.

Enable Input

### **DC Electrical Characteristics**

| Symbol           | Para                              | ameter            |      | ABT240 | 1    | Units | Vcc      | Conditions                                           |

|------------------|-----------------------------------|-------------------|------|--------|------|-------|----------|------------------------------------------------------|

|                  |                                   |                   | Min  | Тур    | Max  | 1     |          |                                                      |

| VIH              | Input HIGH Voltage                |                   | 2.0  |        |      | V     |          | Recognized HIGH Signal                               |

| VIL              | Input LOW Voltage                 |                   |      |        | 0.8  | V     |          | Recognized LOW Signal                                |

| V <sub>CD</sub>  | Input Clamp Diode Vol             | tage              |      |        | -1.2 | V     | Min      | I <sub>IN</sub> = -18 mA                             |

| V <sub>OH</sub>  | Output HIGH Voltage               | 54ABT             | 2.5  |        |      | V     | Min      | I <sub>OH</sub> = -3 mA                              |

|                  |                                   | 54ABT             | 2.0  |        |      | V     | Min      | I <sub>OH</sub> = -24 mA                             |

| V <sub>OL</sub>  | Output LOW Voltage                | 54ABT             |      |        | 0.55 | V     | Min      | I <sub>OL</sub> = 48 mA                              |

| IIH              | Input HIGH Current                |                   |      |        | 5    | μΑ    | Max      | V <sub>IN</sub> = 2.7V (Note 4)                      |

|                  |                                   |                   |      |        | 5    |       |          | $V_{IN} = V_{CC}$                                    |

| I <sub>BVI</sub> | Input HIGH Current Bre            | eakdown Test      |      |        | 7    | μΑ    | Max      | V <sub>IN</sub> = 7.0V                               |

| IIL              | Input LOW Current                 |                   |      |        | -5   | μΑ    | Max      | V <sub>IN</sub> = 0.5V (Note 4)                      |

|                  |                                   |                   |      |        | -5   |       |          | $V_{IN} = 0.0V$                                      |

| VID              | Input Leakage Test                |                   | 4.75 |        |      | V     | 0.0      | I <sub>ID</sub> = 1.9 μA                             |

|                  |                                   |                   |      |        |      |       |          | All Other Pins Grounded                              |

| I <sub>OZH</sub> | Output Leakage Currer             | nt                |      |        | 50   | μΑ    | 0 – 5.5V | $V_{OUT} = 2.7V; \overline{OE}_n = 2.0V$             |

| I <sub>OZL</sub> | Output Leakage Currer             | nt                |      |        | -50  | μA    | 0 – 5.5V | $V_{OUT} = 0.5V; \overline{OE}_n = 2.0V$             |

| los              | Output Short-Circuit Cu           | urrent            | -100 |        | -275 | mA    | Max      | V <sub>OUT</sub> = 0.0V                              |

| ICEX             | Output High Leakage C             | Current           |      |        | 50   | μΑ    | Max      | V <sub>OUT</sub> = V <sub>CC</sub>                   |

| I <sub>ZZ</sub>  | Bus Drainage Test                 |                   |      |        | 100  | μΑ    | 0.0      | V <sub>OUT</sub> = 5.5V; All Others GND              |

| I <sub>CCH</sub> | Power Supply Current              |                   |      |        | 50   | μΑ    | Max      | All Outputs HIGH                                     |

| I <sub>CCL</sub> | Power Supply Current              |                   |      |        | 30   | mA    | Max      | All Outputs LOW                                      |

| I <sub>CCZ</sub> | Power Supply Current              |                   |      |        | 50   | μΑ    | Max      | $\overline{OE}_n = V_{CC};$                          |

|                  |                                   |                   |      |        |      |       |          | All Others at V <sub>CC</sub> or Ground              |

| I <sub>CCT</sub> | Additional I <sub>CC</sub> /Input | Outputs Enabled   |      |        | 1.5  | mA    | Max      | $V_{I} = V_{CC} - 2.1V$                              |

|                  |                                   | Outputs TRI-STATE |      |        | 1.5  | mA    |          | Enable Input V <sub>I</sub> = V <sub>CC</sub> - 2.1V |

|                  |                                   | Outputs TRI-STATE |      |        | 50   | μA    |          | Data Input V <sub>I</sub> = V <sub>CC</sub> – 2.1V   |

|                  |                                   |                   |      |        |      |       |          | All Others at V <sub>CC</sub> or Ground              |

| I <sub>CCD</sub> | Dynamic I <sub>CC</sub>           | No Load           |      |        |      | mA/   | Max      | Outputs Open                                         |

|                  | (Note 4)                          |                   |      |        | 0.1  | MHz   |          | $\overline{OE}_n = GND$ , (Note 3)                   |

|                  |                                   |                   |      |        |      |       |          | One Bit Toggling, 50% Duty Cycle                     |

Note 3: For 8 bits toggling,  $I_{CCD}$  < 0.8 mA/MHz.

Note 4: Guaranteed, but not tested.

20 mV/ns

| Symbol           | Parameter         | 54/                                           | ABT         | Units | Fig.     |

|------------------|-------------------|-----------------------------------------------|-------------|-------|----------|

|                  |                   | T <sub>A</sub> = -55°C                        | C to +125°C | ]     | No.      |

|                  |                   | $V_{CC} = 4.5V-5.5V$<br>$C_L = 50 \text{ pF}$ |             |       |          |

|                  |                   |                                               |             |       |          |

|                  |                   | Min                                           | Max         |       |          |

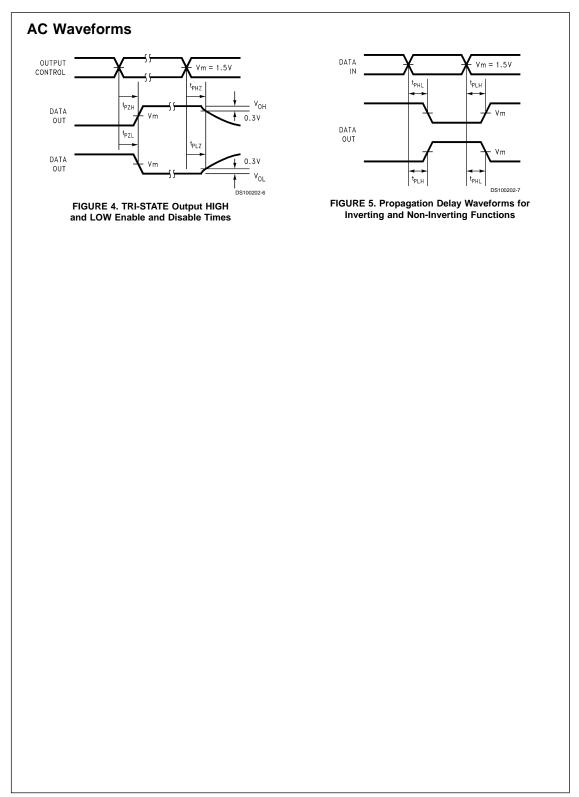

| t <sub>PLH</sub> | Propagation Delay | 0.8                                           | 5.5         | ns    | Figure 5 |

| t <sub>PHL</sub> | Data to Outputs   | 1.0                                           | 5.5         |       |          |

| t <sub>PZH</sub> | Output Enable     | 0.8                                           | 7.5         | ns    | Figure 4 |

| t <sub>PZL</sub> | Time              | 0.8                                           | 7.7         |       |          |

| t <sub>PHZ</sub> | Output Disable    | 1.0                                           | 7.5         | ns    | Figure 4 |

| t <sub>PLZ</sub> | Time              | 1.0                                           | 7.2         |       |          |

# Capacitance

| Symbol                    | Parameter          | Тур | Units | Conditions<br>T <sub>A</sub> = 25°C |

|---------------------------|--------------------|-----|-------|-------------------------------------|

| C <sub>IN</sub>           | Input Capacitance  | 5.0 | pF    | $V_{\rm CC} = 0V$                   |

| C <sub>OUT</sub> (Note 5) | Output Capacitance | 9.0 | pF    | V <sub>CC</sub> = 5.0V              |

Note 5: C<sub>OUT</sub> is measured at frequency f = 1 MHz, per MIL-STD-883B, Method 3012.

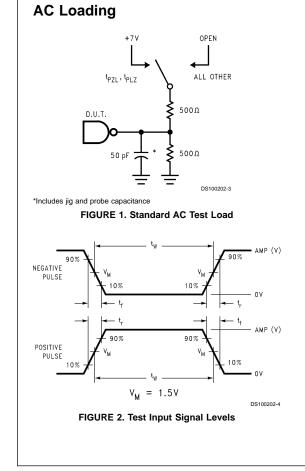

| Amplitude | Rep. Rate | tw     | tr     | t <sub>f</sub> |

|-----------|-----------|--------|--------|----------------|

| 3.0V      | 1 MHz     | 500 ns | 2.5 ns | 2.5 ns         |

FIGURE 3. Test Input Signal Requirements

7