# 1:9 Differential Clock Driver

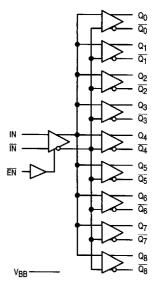

The MC10E/100E111 is a low skew 1-to-9 differential driver, designed with clock distribution in mind. It accepts one signal input, which can be either differential or else single-ended if the VBB output is used. The signal is fanned out to 9 identical differential outputs. An enable input is also provided. A HIGH disables the device by forcing all Q outputs LOW and all  $\overline{\rm Q}$  outputs HIGH.

- Low Skew

- · Guarateed Skew Spec

- Differential Design

- V<sub>BB</sub> Output

- Enable

- Extended 100E VEE Range of -4.2 to -5.46V

- 75kΩ Input Pulldown Resistors

The device is specifically designed, modeled and produced with low skew as the key goal. Optimal design and layout serve to minimize gate to gate skew within-device, and empirical modeling is used to determine process control limits that ensure consistent  $t_{pd}$  distributions from lot to lot. The net result is a dependable, guaranteed low skew device.

To ensure that the tight skew specification is met it is necessary that both sides of the differential output are terminated into  $50\Omega$ , even if only one side is being used. In most applications, all nine differential pairs will be used and therefore terminated. In the case where fewer than nine pairs are used, it is necessary to terminate at least the output pairs on the same package side (i.e. sharing the same VCCO) as the pair(s) being used on that side, in order to maintain minimum skew. Failure to do this will result in small degradations of propagation delay (on the order of 10–20ps) of the output(s) being used which, while not being catastrophic to most designs, will mean a loss of skew margin.

#### **PIN NAMES**

| Pin                                                                                                                                                                                           | Function                                                                |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|

| $\begin{array}{l} \text{IN, } \overline{\text{IN}} \\ \overline{\text{EN}} \\ \text{Q}_0, \overline{\text{Q}_0}\text{-}\text{Q}_8, \overline{\text{Q}_8} \\ \text{V}_{\text{BB}} \end{array}$ | Differential Input Pair<br>Enable<br>Differential Outputs<br>VBB Output |  |  |  |  |  |  |  |

# MC10E111 MC100E111

1:9 DIFFERENTIAL CLOCK DRIVER

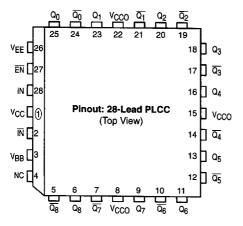

FN SUFFIX PLASTIC PACKAGE CASE 776-02

#### LOGIC SYMBOL

6367252 0099098 032

### MC10E111 MC100E111

### DC CHARACTERISTICS (VEE = VEE (min) to VEE (max); VCC = VCCO = GND)

| Symbol          |                                         | -40°C          |          |                | 0°C            |          |                | 25°C           |          |                | 85°C           |          |                |      |      |

|-----------------|-----------------------------------------|----------------|----------|----------------|----------------|----------|----------------|----------------|----------|----------------|----------------|----------|----------------|------|------|

|                 | Characteristic                          | Min Typ        | Тур      | Max            | Min            | Тур      | Max            | Min            | Тур      | Max            | Min            | Тур      | Max            | Unit | Cond |

| V <sub>BB</sub> | Output Reference<br>Voltage 10E<br>100E | -1.43<br>-1.38 |          | -1.30<br>-1.26 | -1.38<br>-1.38 |          | -1.27<br>-1.26 | -1.35<br>-1.38 |          | -1.25<br>-1.26 | -1.31<br>-1.38 |          | -1.19<br>-1.26 | ٧    |      |

| lін             | Input HIGH<br>Current                   |                |          | 150            |                |          | 150            |                |          | 150            |                |          | 150            | μА   |      |

| <sup> </sup> EE | Power Supply<br>Current 10E<br>100E     |                | 48<br>48 | 60<br>60       |                | 48<br>48 | 60<br>60       |                | 48<br>48 | 60<br>60       |                | 48<br>55 | 60<br>69       | mA   |      |

| VPP(DC)         | Input Sensitivity                       | 50             |          |                | 50             |          |                | 50             |          |                | 50             |          |                | m۷   | 1    |

| VCMR            | Commom Mode<br>Range                    | -1.6           |          | -0.4           | -1.6           |          | -0.4           | -1.6           |          | -0.4           | -1.6           |          | -0.4           | ٧    | 2    |

- 1. Differential input voltage required to obtain a full ECL swing on the outputs.

- 2. V<sub>CMR</sub> is defined as the range within which the V<sub>IH</sub> level may vary, with the device still meeting the propagation delay specification. The V<sub>IL</sub> level must be such that the peak to peak voltage is less than 1.0 V and greater than or equal to Vpp(min).

## AC CHARACTERISTICS (VEE = VEE (min) to VEE (max); VCC = VCCO = GND)

| Symbol                          |                      |           | -40°C |      |     | 0°C |      |     | 25°C |      |     | 85°C |     |     |          |      |

|---------------------------------|----------------------|-----------|-------|------|-----|-----|------|-----|------|------|-----|------|-----|-----|----------|------|

|                                 | Characteristic       |           | Min   | Тур  | Max | Min | Тур  | Max | Min  | Тур  | Max | Min  | Тур | Max | Unit     | Cond |

| <sup>t</sup> PLH                | Propagation Delay to |           |       |      |     |     |      |     |      |      |     |      |     |     | ps       |      |

| tPHL                            | Output               | IN (Diff) | 380   |      | 680 | 460 | ì    | 560 | 480  |      | 580 | 510  |     | 610 | <u> </u> | 1    |

| –                               |                      | IN (SE)   | 280   |      | 780 | 410 |      | 610 | 430  |      | 630 | 460  | ŀ   | 660 |          | 2    |

|                                 |                      | Enable    | 400   |      | 900 | 450 | j    | 850 | 450  |      | 850 | 450  | 1   | 850 | Į.       | 3    |

|                                 |                      | Disable   | 400   |      | 900 | 450 |      | 850 | 450  |      | 850 | 450  |     | 850 |          | 3    |

| ts                              | Setup Time           | EN to IN  | 250   | 0    |     | 200 | 0    |     | 200  | 0    |     | 200  | 0   |     | ps       | 5    |

| tH                              | Hold Time            | IN to EN  | 50    | -200 |     | 0   | -200 |     | 0    | -200 |     | 0    | 200 |     | ps       | 6    |

| t <sub>R</sub>                  | Release Time         | EN to IN  | 350   | 100  |     | 300 | 100  |     | 300  | 100  |     | 300  | 100 |     | ps       | 7    |

| t <sub>skew</sub>               | Within-Device Skew   |           |       | 25   | 75  |     | 25   | 50  |      | 25   | 50  |      | 25  | 50  | ps       | 4    |

| V <sub>PP</sub> (AC)            | Minimum Input Swing  |           | 250   |      |     | 250 |      |     | 250  |      |     | 250  |     |     | mV       | 8    |

| t <sub>r</sub> , t <sub>f</sub> | Rise/Fall Time       |           | 250   | 450  | 650 | 275 | 375  | 600 | 275  | 375  | 600 | 275  | 375 | 600 | ps       |      |

- 1. The differential propagation delay is defined as the delay from the crossing points of the differential input signals to the crossing point of the differential output signals. See Definitions and Testing of ECLinPS AC Parameters in Chapter 1 (page 1-12) of the Motorola High Performance ECL Data Book (DL140/D).

- 2. The single-ended propagation delay is defined as the delay from the 50% point of the input signal to the 50% point of the output signal. See Definitions and Testing of ECLinPS AC Parameters in Chapter 1 (page 1-12) of the Motorola High Performance ECL Data Book (DL140/D).

- 3. Enable is defined as the propagation delay from the 50% point of a negative transition on EN to the 50% point of a positive transition on Q (or a negative transition on  $\overline{Q}$ ). Disable is defined as the propagation delay from the 50% point of a **positive** transition on  $\overline{EN}$  to the 50% point of a **negative** transition on Q (or a positive transition on  $\overline{Q}$ ).

- The within-device skew is defined as the worst case difference between any two similar delay paths within a single device.

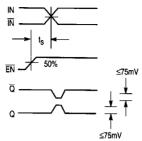

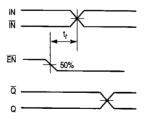

The setup time is the minimum time that EN must be asserted prior to the next transition of IN/IN to prevent an output response greater than

- ±75 mV to that IN/IN transition (see Figure 1).

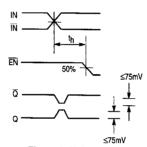

6. The hold time is the minimum time that EN must remain asserted after a negative going IN or a positive going IN to prevent an output response greater than  $\pm 75$  mV to that  $IN/\overline{IN}$  transition (see Figure 2).

- 7. The release time is the minimum time that EN must be deasserted prior to the next IN/IN transition to ensure an output response that meets the specified IN to Q propagation delay and output transition times (see Figure 3).

- Vpp(min) is defined as the minimum input differential voltage which will cause no increase in the propagation delay. The Vpp(min) is AC limited for the E111 as a differential input as low as 50 mV will still produce full ECL levels at the output.

Figure 1. Setup Time

Figure 2. Hold Time

Figure 3. Release Time