# QT1040 /QT1020 4GB Qormino Integrated Multicore Communications Processor with 4GB of DDR4

**Datasheet preliminary DS1195**

#### **FEATURES**

- · 4GB of DDR4 with ECC

- e5500 cores built on Power Architecture® technology,

- QT1040 has four cores and QT1020 has two cores

- Each core with a private 256KB L2 cache

- 256 KB shared L3 CoreNet platform cache (CPC)

- · Hierarchical interconnect fabric

- CoreNet Coherency manager supporting coherent and noncoherent transactions with prioritization and bandwidth allocation amongst CoreNet end-points

- 150Gbps coherent read bandwidthData Path Acceleration Architecture (DPAA) incorporating acceleration for the following functions:

- Packet parsing, classification, and distribution

- Queue management for scheduling, packet sequencing, and congestion management

- Hardware buffer management for buffer allocation and deallocation

- Cryptography Acceleration

- RegEx Pattern Matching Acceleration

- IEEE Std 1588<sup>™</sup> support

- · Integrated 8-port Gigabit Ethernet switch

- 8K MAC addresses, 4K VLANs

- Static Address provisioning

- Dynamic learning of MAC addresses and aging

- Policing with storm control and MC/BC protection

- Link aggregation (IEEE Std 802.3ad)

- Spanning Tree Protocol (STP, RSTP and MSTP)

- Access Control List

- VLAN editing, translation and remarking

- Hierarchical QoS with DWRR scheduling

- · Parallel Ethernet interfaces

- Up to two RGMII interface

- One MII interface

- Eight SerDes lanes for high-speed peripheral interfaces

- Four PCI Express 2.0 controllers

- Two Serial ATA (SATA 3Gb/s) controllers

- Up to two QSGMII interface

- Up to six SGMII interface supporting 1000 Mbps

- Supports 1000Base-KX

- · Additional peripheral interfaces

- Two high-speed USB 2.0 controllers with integrated PHY

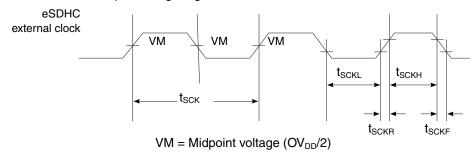

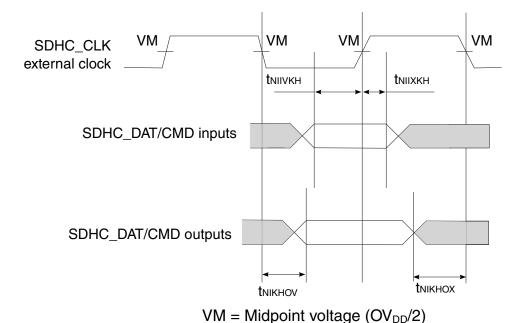

- Enhanced secure digital host controller with support for high capacity memory card (SD/eSDHC/eMMC)

- Enhanced Serial peripheral interface (eSPI)

- Four I2C controllers

- Two DUARTs

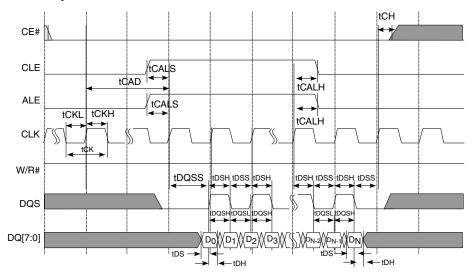

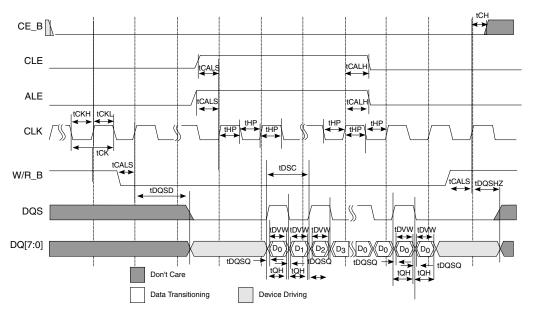

- Integrated flash controller supporting NAND and NOR flash

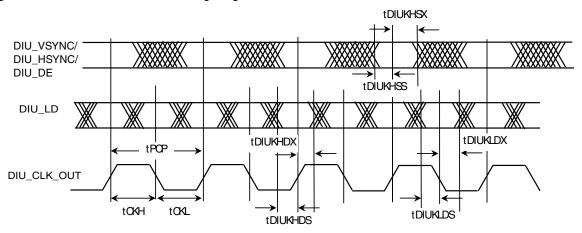

- Display interface unit (DIU) with 12-bit dual data rate

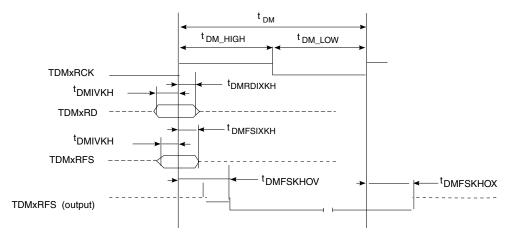

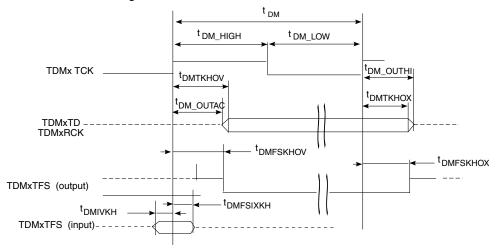

- TDM Interface

- Four GPIO controllers supporting up to 109 general purpose I/O signals

- Two 8-channel DMA engines

- Multicore programmable interrupt controller (MPIC)

- · QUICC Engine block

- 32-bit RISC controller for flexible support of the communications peripherals

- Serial DMA channel for receive and transmit on all serial channels

- Two universal communication controllers, supporting TDM, HDLC and UART

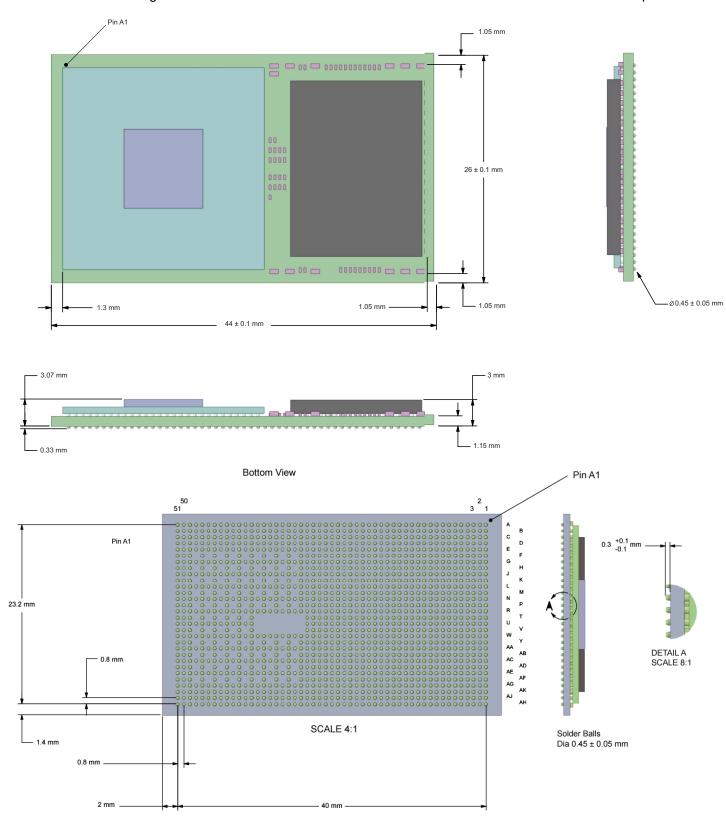

- Package: 26 × 44 mm, 1415 solder spheres pitch 0.8 mm

#### **OVERVIEW**

The QT1040 QorlQ advanced multicore processor combines four 64-bit ISA Power Architecture<sup>™</sup> processor cores with high-performance data path acceleration and network and peripheral bus interfaces required for networking, telecom/datacom, wireless infrastructure, and military/aerospace applications.

This chip can be used for combined control, data path, and application layer processing in routers, switches, gateways, and general-purpose embedded computing systems. Its high level of integration offers significant performance benefits compared to multiple discrete devices, while also simplifying board design.

Holding Company: Teledyne e2v Semiconductors SAS

Whilst Teledyne e2v Semiconductors SAS has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Teledyne e2v Semiconductors SAS accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of the devices in accordance with information contained herein.

Teledyne e2v Semiconductors SAS, avenue de Rochepleine 38120 Saint-Egrève, France

Telephone: +33 (0)4 76 58 30 00

Contact Teledyne e2v by e-mail: hotline-std@teledyne-e2v.com or visit www.teledyne-e2v.com for global sales and operations centres

1195F-HIREL-05/19

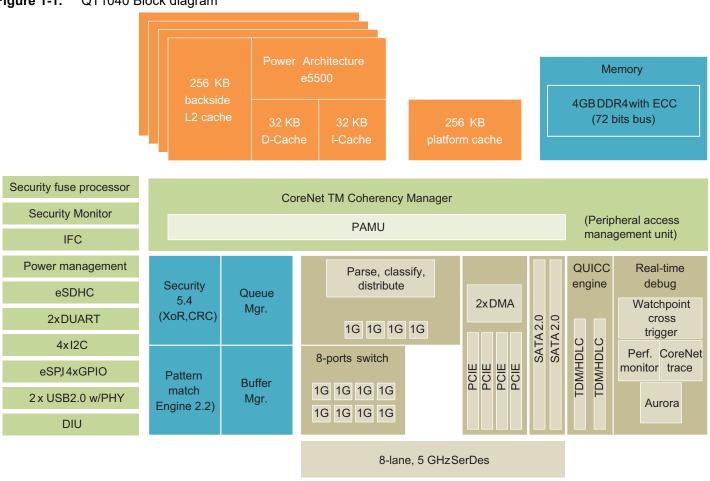

This figure shows the block diagram of the chip.

#### 1. BLOCK DIAGRAM

Figure 1-1. QT1040 Block diagram

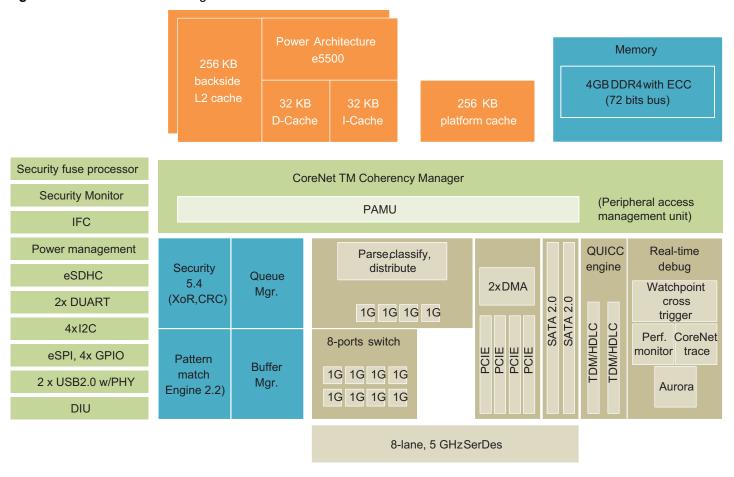

Figure 1-2. QT1020 Block diagram

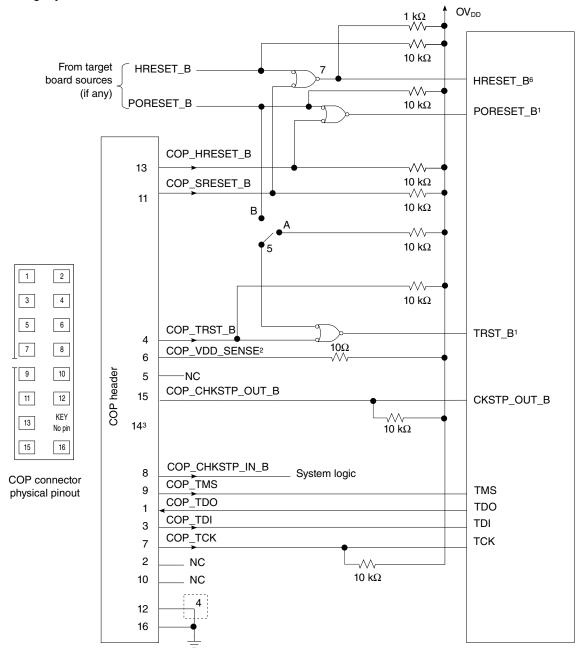

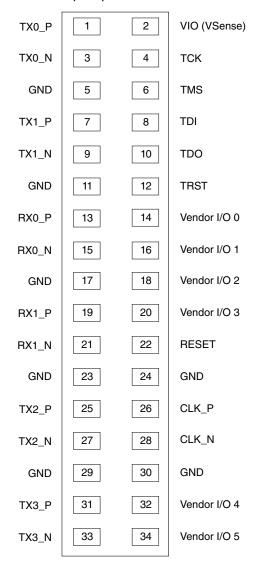

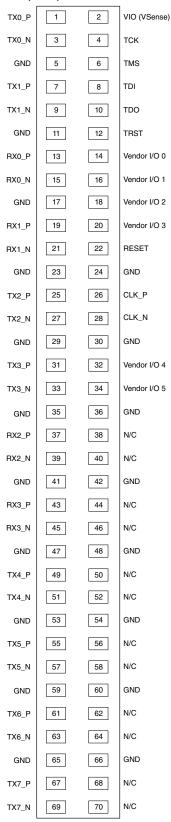

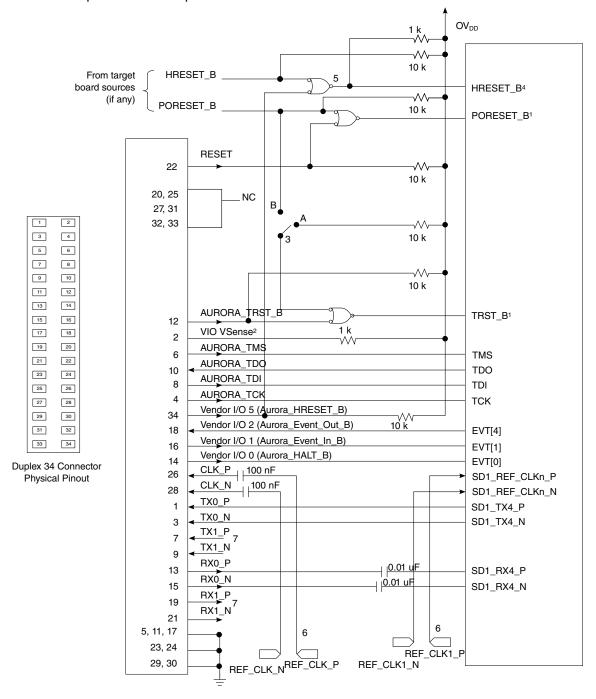

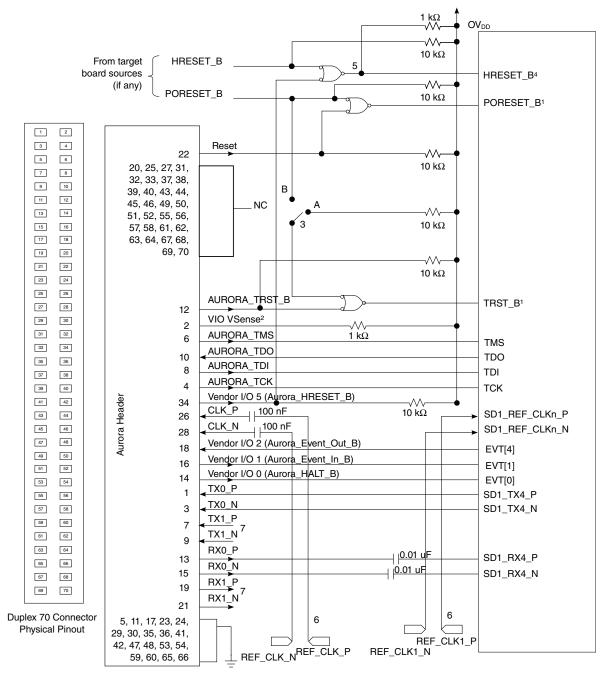

#### 2. PIN ASSIGNMENTS

#### 2.1 Layout diagrams

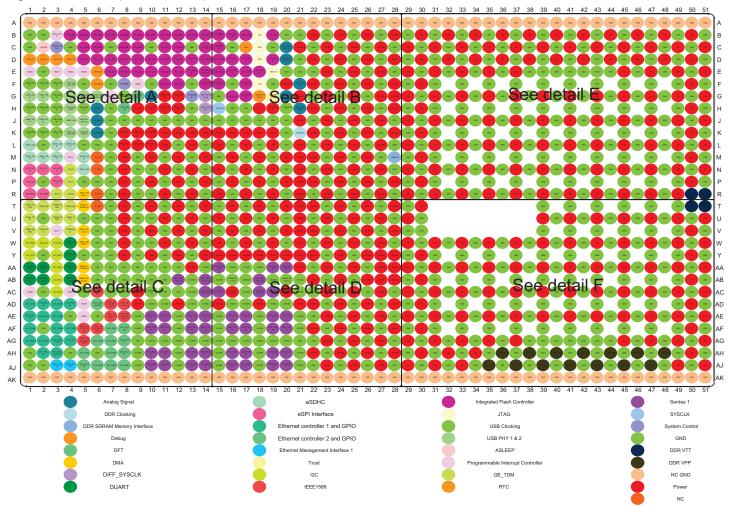

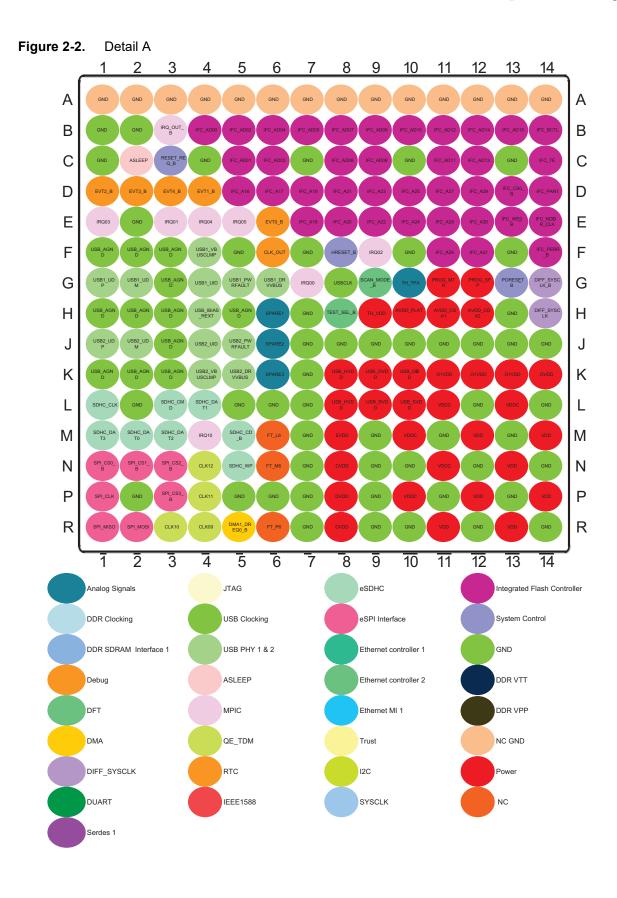

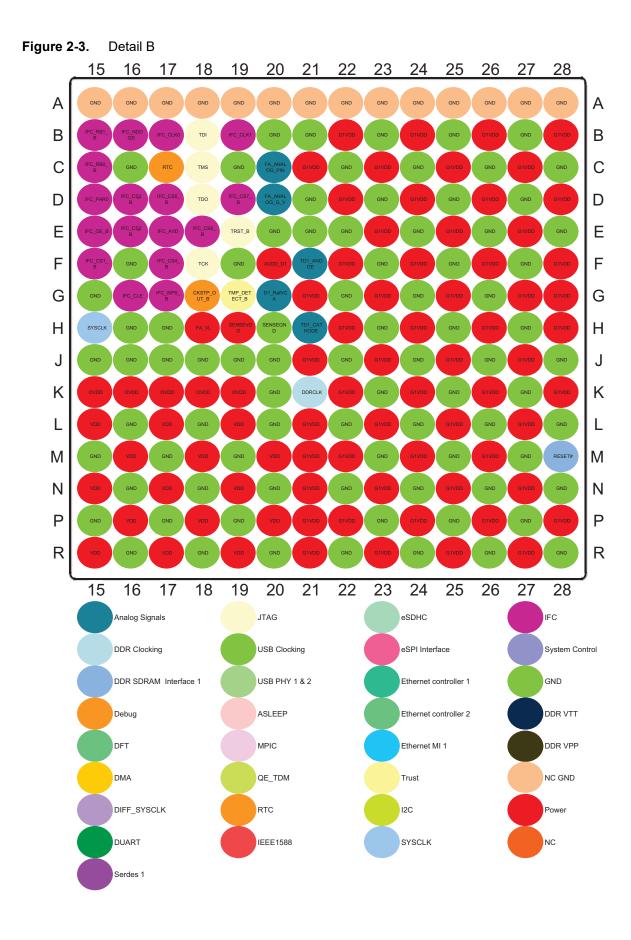

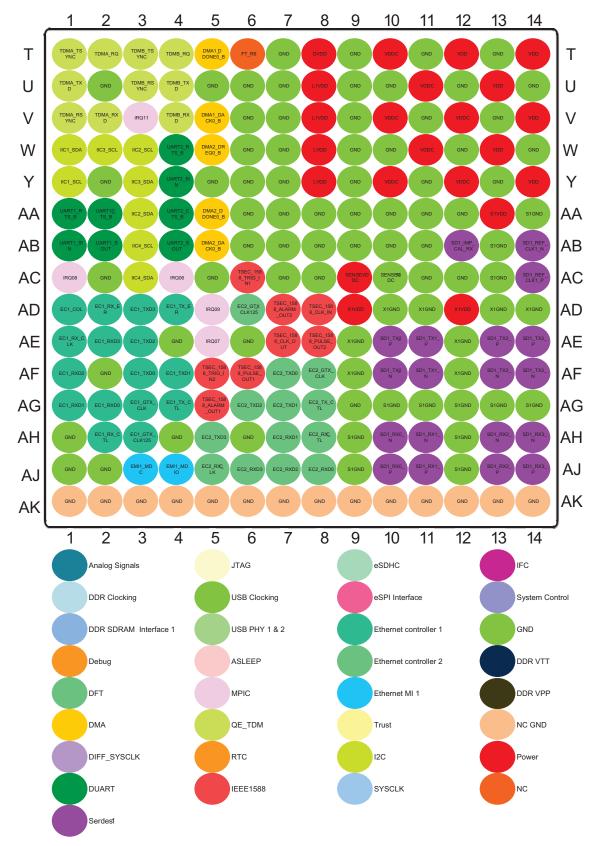

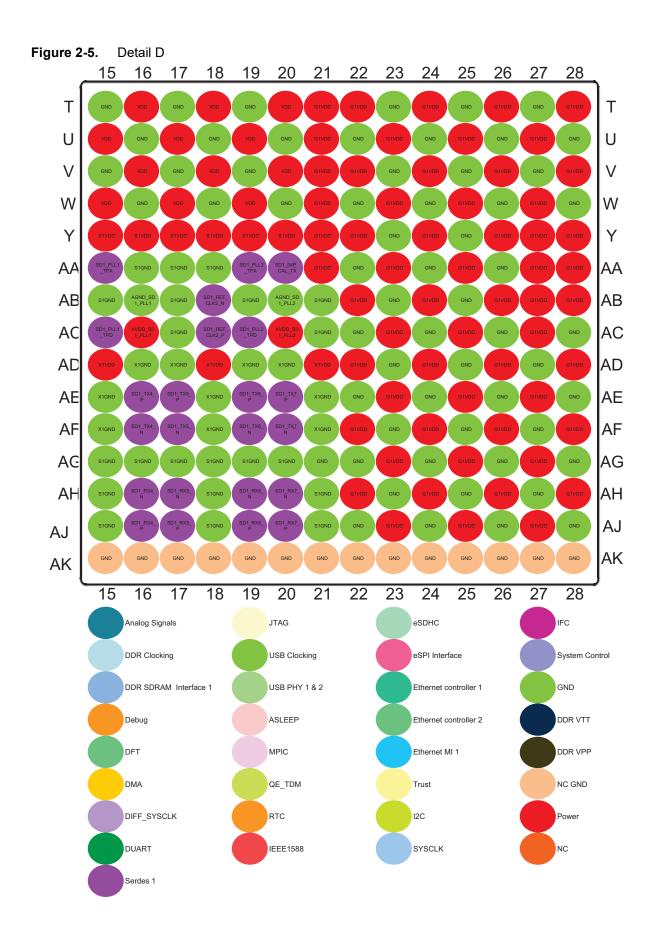

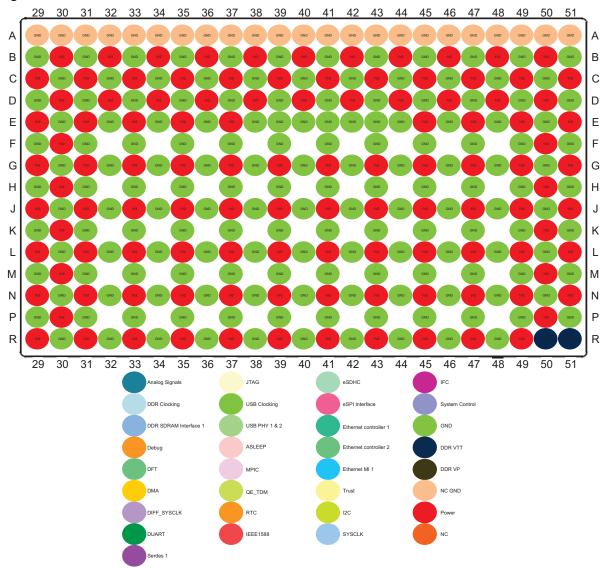

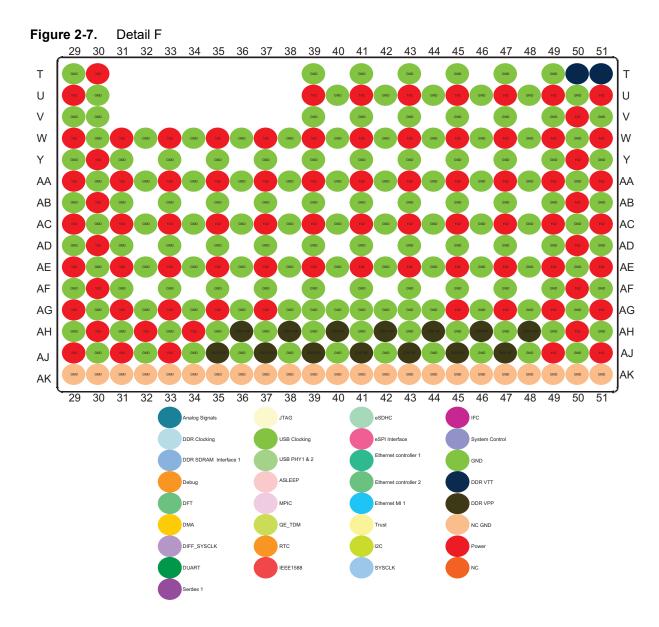

This figure shows the complete view of the QT1040 ball map diagram. Figure 2-2, Figure 2-3, Figure 2-4, and Figure 2-5 show quadrant views.

Figure 2-1. Complete BGA Map for the QT1040

Figure 2-4. Detail C

Figure 2-6. Detail E

#### 2.2 Pinout list

This table provides the pinout listing for the QT1040 by bus. Primary functions are **bolded** in the table.

Table 2-1. Pinout List

| Signal                     | Signal description          | Package pin<br>number | Pin type | Power supply | Notes  |

|----------------------------|-----------------------------|-----------------------|----------|--------------|--------|

|                            | DDR SDRAM Memory Interface  | 1                     |          |              |        |

| RESET#                     | DDR Reset#                  | M28                   | 1        | G1VDD        | _      |

|                            | Integrated Flash Controller |                       |          |              |        |

| IFC_A16                    | IFC Address                 | D5                    | 0        | OVDD         | (1)(5) |

| IFC_A17                    | IFC Address                 | D6                    | 0        | OVDD         | (1)(5) |

| IFC_A18                    | IFC Address                 | E7                    | 0        | OVDD         | (1)(5) |

| IFC_A19                    | IFC Address                 | D7                    | 0        | OVDD         | (1)(5) |

| IFC_A20                    | IFC Address                 | E8                    | 0        | OVDD         | (1)(5) |

| IFC_A21/cfg_dram_type      | IFC Address                 | D8                    | 0        | OVDD         | (1)(4) |

| IFC_A22                    | IFC Address                 | E9                    | 0        | OVDD         | (1)    |

| IFC_A23                    | IFC Address                 | D9                    | 0        | OVDD         | (1)    |

| IFC_A24                    | IFC Address                 | E10                   | 0        | OVDD         | (1)    |

| IFC_A25/GPIO2_25/IFC_WP1_B | IFC Address                 | D10                   | 0        | OVDD         | (1)    |

| IFC_A26/GPIO2_26/IFC_WP2_B | IFC Address                 | F11                   | 0        | OVDD         | (1)    |

| IFC_A27/GPIO2_27/IFC_WP3_B | IFC Address                 | D11                   | 0        | OVDD         | (1)    |

| IFC_A28/GPIO2_28           | IFC Address                 | E11                   | 0        | OVDD         | (1)    |

| IFC_A29/GPIO2_29/IFC_RB2_B | IFC Address                 | D12                   | 0        | OVDD         | (1)    |

| IFC_A30/GPIO2_30/IFC_RB3_B | IFC Address                 | E12                   | 0        | OVDD         | (1)    |

| IFC_A31/GPIO2_31/IFC_RB4_B | IFC Address                 | F12                   | 0        | OVDD         | (1)    |

| IFC_AD00/cfg_gpinput0      | IFC Address / Data          | B4                    | Ю        | OVDD         | (4)    |

| IFC_AD01/cfg_gpinput1      | IFC Address / Data          | C5                    | Ю        | OVDD         | (4)    |

| IFC_AD02/cfg_gpinput2      | IFC Address / Data          | B5                    | Ю        | OVDD         | (4)    |

| IFC_AD03/cfg_gpinput3      | IFC Address / Data          | C6                    | Ю        | OVDD         | (4)    |

| IFC_AD04/cfg_gpinput4      | IFC Address / Data          | B6                    | Ю        | OVDD         | (4)    |

| IFC_AD05/cfg_gpinput5      | IFC Address / Data          | В7                    | Ю        | OVDD         | (4)    |

| IFC_AD06/cfg_gpinput6      | IFC Address / Data          | C8                    | Ю        | OVDD         | (4)    |

| IFC_AD07/cfg_gpinput7      | IFC Address / Data          | B8                    | 10       | OVDD         | (4)    |

| IFC_AD08/cfg_rcw_src0      | IFC Address / Data          | C9                    | Ю        | OVDD         | (4)    |

| IFC_AD09/cfg_rcw_src1      | IFC Address / Data          | B9                    | 10       | OVDD         | (4)    |

| IFC_AD10/cfg_rcw_src2      | IFC Address / Data          | B10                   | 10       | OVDD         | (4)    |

| IFC_AD11/cfg_rcw_src3      | IFC Address / Data          | C11                   | 10       | OVDD         | (4)    |

| IFC_AD12/cfg_rcw_src4      | IFC Address / Data          | B11                   | Ю        | OVDD         | (4)    |

| IFC_AD13/cfg_rcw_src5      | IFC Address / Data          | C12                   | Ю        | OVDD         | (4)    |

| IFC_AD14/cfg_rcw_src6      | IFC Address / Data          | B12                   | Ю        | OVDD         | (4)    |

| IFC_AD15/cfg_rcw_src7      | IFC Address / Data          | B13                   | Ю        | OVDD         | (4)    |

| IFC_AVD                    | IFC Address Valid           | E17                   | 0        | OVDD         | (1)(5) |

| IFC_BCTL                   | IFC Buffer control          | B14                   | 0        | OVDD         | (1)    |

Table 2-1.Pinout List (Continued)

| Signal                                   | Signal description              | Package pin<br>number | Pin type | Power supply | Notes   |

|------------------------------------------|---------------------------------|-----------------------|----------|--------------|---------|

| IFC_CLE/cfg_rcw_src8                     | IFC Command Latch Enable        | G16                   | 0        | OVDD         | (1)(4)  |

| IFC_CLK0                                 | IFC Clock                       | B17                   | 0        | OVDD         | (1)     |

| IFC_CLK1                                 | IFC Clock                       | B19                   | 0        | OVDD         | (1)     |

| IFC_CS0_B                                | IFC Chip Select                 | D13                   | 0        | OVDD         | (1)(6)  |

| IFC_CS1_B/GPIO2_10                       | IFC Chip Select                 | F15                   | 0        | OVDD         | (1)(6)  |

| IFC_CS2_B/GPIO2_11                       | IFC Chip Select                 | E16                   | 0        | OVDD         | (1)(6)  |

| IFC_CS3_B/GPIO2_12                       | IFC Chip Select                 | D16                   | 0        | OVDD         | (1)(6)  |

| IFC_CS4_B/GPIO1_09                       | IFC Chip Select                 | F17                   | 0        | OVDD         | (1)(6)  |

| IFC_CS5_B/GPIO1_10                       | IFC Chip Select                 | D17                   | 0        | OVDD         | (1)(6)  |

| IFC_CS6_B/GPIO1_11                       | IFC Chip Select                 | E18                   | 0        | OVDD         | (1)(6)  |

| IFC_CS7_B/GPIO1_12                       | IFC Chip Select                 | D19                   | 0        | OVDD         | (1)(6)  |

| IFC_NDDDR_CLK                            | IFC NAND DDR Clock              | E14                   | 0        | OVDD         | (1)     |

| IFC_NDDQS                                | IFC DQS Strobe                  | B16                   | Ю        | OVDD         | _       |

| IFC_OE_B/cfg_eng_use1                    | IFC Output Enable               | E15                   | 0        | OVDD         | (1)(22) |

| IFC_PAR0/GPIO2_13                        | IFC Address & Data Parity       | D15                   | Ю        | OVDD         | _       |

| IFC_PAR1/GPIO2_14                        | IFC Address & Data Parity       | D14                   | Ю        | OVDD         | _       |

| IFC_PERR_B/GPIO2_15                      | IFC Parity Error                | F14                   | I        | OVDD         | (1)(6)  |

| IFC_RB2_B/ <b>IFC_A29</b> /GPIO2_29      | IFC Ready / Busy CS 2           | D12                   | I        | OVDD         | (1)     |

| IFC_RB3_B/ <b>IFC_A30</b> /GPIO2_30      | IFC Ready / Busy CS 3           | E12                   | I        | OVDD         | (1)     |

| IFC_RB4_B/ <b>IFC_A31</b> /GPIO2_31      | IFC Ready / Busy CS 4           | F12                   | I        | OVDD         | (1)     |

| IFC_RB0_B                                | IFC Ready / Busy CS0            | C15                   | I        | OVDD         | (6)     |

| IFC_RB1_B                                | IFC Ready / Busy CS1            | B15                   | I        | OVDD         | (6)     |

| IFC_TE/cfg_ifc_te                        | IFC External Transceiver Enable | C14                   | 0        | OVDD         | (1)(4)  |

| IFC_WE0_B/cfg_eng_use0                   | IFC Write Enable                | E13                   | 0        | OVDD         | (1)(22) |

| IFC_WP1_B/ <b>IFC_A25</b> /GPIO2_25      | IFC Write Protect               | D10                   | 0        | OVDD         | (1)     |

| IFC_WP2_B/IFC_A26/GPIO2_26               | IFC Write Protect               | F11                   | 0        | OVDD         | (1)     |

| IFC_WP3_B/ <b>IFC_A27</b> /GPIO2_27      | IFC Write Protect               | D11                   | 0        | OVDD         | (1)     |

| IFC_WP0_B/cfg_eng_use2                   | IFC Write Protect               | G17                   | 0        | OVDD         | (1)(22) |

|                                          | DUART                           |                       |          |              |         |

| UART1_CTS_B/GPIO1_21/UART3_SIN           | Clear To Send                   | AA2                   | I        | DVDD         | (1)     |

| UART1_RTS_B/GPIO1_19/UART3_SOUT          | Ready to Send                   | AA1                   | 0        | DVDD         | (1)     |

| UART1_SIN/GPIO1_17                       | Receive Data                    | AB1                   | I        | DVDD         | (1)     |

| UART1_SOUT/GPIO1_15                      | Transmit Data                   | AB2                   | 0        | DVDD         | (1)     |

| UART2_CTS_B/GPIO1_22/UART4_SIN           | Clear To Send                   | AA4                   | I        | DVDD         | (1)     |

| UART2_RTS_B/GPIO1_20/UART4_SOUT          | Ready to Send                   | W4                    | 0        | DVDD         | (1)     |

| UART2_SIN/GPIO1_18                       | Receive Data                    | Y4                    | I        | DVDD         | (1)     |

| UART2_SOUT/GPIO1_16                      | Transmit Data                   | AB4                   | 0        | DVDD         | (1)     |

| UART3_SIN/ <b>UART1_CTS_B</b> /GPIO1_21  | Receive Data                    | AA2                   | I        | DVDD         | (1)     |

| UART3_SOUT/ <b>UART1_RTS_B</b> /GPIO1_19 | Transmit Data                   | AA1                   | 0        | DVDD         | (1)     |

| UART4_SIN/ <b>UART2_CTS_B</b> /GPIO1_22  | Receive Data                    | AA4                   | I        | DVDD         | (1)     |

Table 2-1.Pinout List (Continued)

| Signal                                                             | Signal description              | Package pin<br>number | Pin type | Power supply | Notes     |

|--------------------------------------------------------------------|---------------------------------|-----------------------|----------|--------------|-----------|

| UART4_SOUT/ <b>UART2_RTS_B</b> /GPIO1_20                           | Transmit Data                   | W4                    | 0        | DVDD         | (1)       |

|                                                                    | I2C                             |                       |          |              |           |

| IIC1_SCL                                                           | Serial Clock (supports PBL)     | Y1                    | Ю        | DVDD         | (7)(8)    |

| IIC1_SDA                                                           | Serial Data (supports PBL)      | W1                    | Ю        | DVDD         | (7)(8)    |

| IIC2_SCL                                                           | Serial Clock                    | W3                    | Ю        | DVDD         | (7)(8)    |

| IIC2_SDA                                                           | Serial Data                     | AA3                   | Ю        | DVDD         | (7)(8)    |

|                                                                    | eSPI Interface                  |                       |          |              |           |

| SPI_CLK                                                            | SPI Clock                       | P1                    | 0        | CVDD         | (1)       |

| SPI_CS0_B/GPIO2_00/SDHC_DAT4                                       | SPI Chip Select                 | N1                    | 0        | CVDD         | (1)       |

| SPI_CS1_B/GPIO2_01/SDHC_DAT5/SDHC_CMD_DIR                          | SPI Chip Select                 | N2                    | 0        | CVDD         | (1)       |

| SPI_CS2_B/GPIO2_02/SDHC_DAT6/SDHC_DAT0_DIR                         | SPI Chip Select                 | N3                    | 0        | CVDD         | (1)       |

| SPI_CS3_B/GPIO2_03/SDHC_DAT7/SDHC_DAT123_DIR/<br>SDHC_CLK_SYNC_OUT | SPI Chip Select                 | Р3                    | 0        | CVDD         | (1)       |

| SPI_MISO                                                           | Master In Slave Out             | R1                    | Ι        | CVDD         | (1)       |

| SPI_MOSI                                                           | Master Out Slave In             | R2                    | Ю        | CVDD         | -         |

|                                                                    | Programmable Interrupt Controll | er                    |          |              |           |

| IRQ00                                                              | External Interrupt              | G7                    | I        | O1VDD        | (1)       |

| IRQ01                                                              | External Interrupt              | E3                    | I        | O1VDD        | (1)       |

| IRQ02                                                              | External Interrupt              | F9                    | I        | O1VDD        | (1)       |

| IRQ03/GPIO1_23/SDHC_VS                                             | External Interrupt              | E1                    | I        | O1VDD        | (1)       |

| IRQ04/GPIO1_24                                                     | External Interrupt              | E4                    | I        | O1VDD        | (1)       |

| IRQ05/GPIO1_25                                                     | External Interrupt              | E5                    | Ι        | O1VDD        | (1)       |

| IRQ06/GPIO1_26                                                     | External Interrupt              | AC4                   | I        | L1VDD        | (1)       |

| IRQ07/GPIO1_27                                                     | External Interrupt              | AE5                   | I        | L1VDD        | (1)       |

| IRQ08/GPIO1_28                                                     | External Interrupt              | AC1                   | I        | L1VDD        | (1)       |

| IRQ09/GPIO1_29                                                     | External Interrupt              | AD5                   | I        | L1VDD        | (1)       |

| IRQ10/GPIO1_30/SDHC_CLK_SYNC_IN                                    | External Interrupt              | M4                    | I        | CVDD         | (1)       |

| IRQ11/GPIO1_31                                                     | External Interrupt              | V3                    | I        | DVDD         | (1)       |

| IRQ_OUT_B/EVT9_B                                                   | Interrupt Output                | В3                    | 0        | O1VDD        | (1)(6)(7) |

|                                                                    | Trust                           |                       |          |              |           |

| TMP_DETECT_B                                                       | Tamper Detect                   | G19                   | I        | OVDD         | (1)       |

|                                                                    | System Control                  |                       |          |              |           |

| HRESET_B                                                           | Hard Reset                      | F8                    | Ю        | O1VDD        | (7)(27)   |

| PORESET_B                                                          | Power On Reset                  | G13                   | I        | O1VDD        | (26)      |

| RESET_REQ_B                                                        | Reset Request (POR or Hard)     | C3                    | 0        | O1VDD        | (1)(5)    |

|                                                                    | Power Management                |                       |          | 1            | 1         |

| ASLEEP/GPO1_13                                                     | Asleep                          | C2                    | 0        | O1VDD        | (1)       |

|                                                                    | SYSCLK                          | ı                     | <u> </u> | 1            | 1         |

| SYSCLK                                                             | System Clock                    | H15                   | I        | O1VDD        | (1)(7)    |

|                                                                    | DDR Clocking                    | 1                     |          | 1            | 1         |

Table 2-1. Pinout List (Continued)

| Signal                                         | Signal description                    | Package pin<br>number | Pin type | Power supply      | Notes     |

|------------------------------------------------|---------------------------------------|-----------------------|----------|-------------------|-----------|

| DDRCLK                                         | DDR Controller Clock                  | K21                   | 1        | OVDD              | (1)(7)    |

|                                                | RTC                                   |                       |          |                   |           |

| RTC/GPIO1_14                                   | Real Time Clock                       | C17                   | 1        | OVDD              | (1)       |

|                                                | Debug                                 |                       |          |                   |           |

| CKSTP_OUT_B                                    | Checkstop Out                         | G18                   | 0        | OVDD              | (1)(6)(7) |

| CLK_OUT                                        | Clock Out                             | F6                    | 0        | O1VDD             | _         |

| EVT5_B/IIC4_SCL/GPIO4_02/DIU_HSYNC             | Event 5                               | AB3                   | 10       | DVDD              | _         |

| EVT6_B/IIC4_SDA/GPIO4_03/DIU_VSYNC             | Event 6                               | AC3                   | Ю        | DVDD              | _         |

| EVT7_B/ <b>DMA2_DACK0_B</b> /GPIO4_08/TDM_RFS  | Event 7                               | AB5                   | Ю        | DVDD              | _         |

| EVT8_B/ <b>DMA2_DDONE0_B</b> /GPIO4_09/TDM_RCK | Event 8                               | AA5                   | Ю        | DVDD              | _         |

| EVT9_B/ <b>IRQ_OUT_B</b>                       | Event 9                               | В3                    | Ю        | O1VDD             | _         |

| EVT0_B                                         | Event 0                               | E6                    | Ю        | O1VDD             | (9)       |

| EVT1_B                                         | Event 1                               | D4                    | Ю        | O1VDD             | _         |

| EVT2_B                                         | Event 2                               | D1                    | Ю        | O1VDD             | (6)(22)   |

| EVT3_B                                         | Event 3                               | D2                    | Ю        | O1VDD             | _         |

| EVT4_B                                         | Event 4                               | D3                    | Ю        | O1VDD             | _         |

|                                                | DFT                                   |                       |          | 1                 |           |

| SCAN_MODE_B                                    | Reserved                              | G9                    | 1        | O1VDD             | (10)      |

| TEST_SEL_B                                     | Reserved                              | H8                    | 1        | O1VDD             | (23)      |

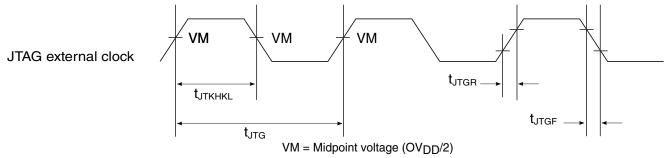

|                                                | JTAG                                  |                       |          |                   |           |

| тск                                            | Test Clock                            | F18                   | 1        | OVDD              | _         |

| TDI                                            | Test Data In                          | B18                   | I        | OVDD              | (9)       |

| TDO                                            | Test Data Out                         | D18                   | 0        | OVDD              | _         |

| TMS                                            | Test Mode Select                      | C18                   | 1        | OVDD              | (9)       |

| TRST_B                                         | Test Reset                            | E19                   | 1        | OVDD              | (9)       |

|                                                | Analog Signals                        |                       |          | 1                 |           |

| D1_MVREF                                       | SSTL Reference Voltage                | G20                   | 10       | G1VDD/2           | _         |

| FA_ANALOG_G_V                                  | Reserved for internal use only        | D20                   | Ю        | _                 | (15)      |

| FA_ANALOG_PIN                                  | Reserved for internal use only        | C20                   | Ю        | _                 | (15)      |

| SPARE1                                         | Reserved for internal use only        | H6                    | -        | _                 | (12)      |

| SPARE2                                         | Reserved for internal use only        | J6                    | -        | _                 | (12)      |

| SPARE3                                         | Reserved for internal use only        | K6                    | -        | -                 | (12)      |

| TD1_ANODE                                      | Thermal diode anode                   | F21                   | Ю        |                   | (19)      |

| TD1_CATHODE                                    | Thermal diode cathode                 | H21                   | Ю        |                   | (19)      |

| TH_TPA                                         | Reserved for internal use only        | G10                   | -        | _                 | (12)      |

|                                                | Serdes 1                              |                       |          | •                 |           |

| SD1_IMP_CAL_RX                                 | SerDes Receive Impedence Calibration  | AB12                  | I        | S1VDD             | (11)      |

| SD1_IMP_CAL_TX                                 | SerDes Transmit Impedance Calibration | AA20                  | I        | X1VDD             | (16)      |

| SD1_PLL1_TPA                                   | Reserved for internal use only        | AA15                  | 0        | AVDD_SD1_PL<br>L1 | (12)      |

Table 2-1.Pinout List (Continued)

| Signal         | Signal description                         | Package pin<br>number | Pin type | Power supply      | Notes |

|----------------|--------------------------------------------|-----------------------|----------|-------------------|-------|

| SD1_PLL1_TPD   | Reserved for internal use only             | AC15                  | 0        | X1VDD             | (12)  |

| SD1_PLL2_TPA   | Reserved for internal use only             | AA19                  | 0        | AVDD_SD1_PL<br>L2 | (12)  |

| SD1_PLL2_TPD   | Reserved for internal use only             | AC19                  | 0        | X1VDD             | (12)  |

| SD1_REF_CLK1_N | SerDes PLL 1 Reference Clock<br>Complement | AB14                  | I        | S1VDD             | _     |

| SD1_REF_CLK1_P | SerDes PLL 1 Reference Clock               | AC14                  | 1        | S1VDD             | -     |

| SD1_REF_CLK2_N | SerDes PLL 2 Reference Clock<br>Complement | AB18                  | I        | S1VDD             | _     |

| SD1_REF_CLK2_P | SerDes PLL 2 Reference Clock               | AC18                  | 1        | S1VDD             | -     |

| SD1_RX0_N      | SerDes Receive Data (negative)             | AH10                  | I        | S1VDD             | -     |

| SD1_RX0_P      | SerDes Receive Data (positive)             | AJ10                  | I        | S1VDD             | -     |

| SD1_RX1_N      | SerDes Receive Data (negative)             | AH11                  | I        | S1VDD             | -     |

| SD1_RX1_P      | SerDes Receive Data (positive)             | AJ11                  | I        | S1VDD             | -     |

| SD1_RX2_N      | SerDes Receive Data (negative)             | AH13                  | I        | S1VDD             | -     |

| SD1_RX2_P      | SerDes Receive Data (positive)             | AJ13                  | I        | S1VDD             | -     |

| SD1_RX3_N      | SerDes Receive Data (negative)             | AH14                  | I        | S1VDD             | -     |

| SD1_RX3_P      | SerDes Receive Data (positive)             | AJ14                  | I        | S1VDD             | -     |

| SD1_RX4_N      | SerDes Receive Data (negative)             | AH16                  | I        | S1VDD             | -     |

| SD1_RX4_P      | SerDes Receive Data (positive)             | AJ16                  | I        | S1VDD             | -     |

| SD1_RX5_N      | SerDes Receive Data (negative)             | AH17                  | I        | S1VDD             | -     |

| SD1_RX5_P      | SerDes Receive Data (positive)             | AJ17                  | I        | S1VDD             | -     |

| SD1_RX6_N      | SerDes Receive Data (negative)             | AH19                  | I        | S1VDD             | -     |

| SD1_RX6_P      | SerDes Receive Data (positive)             | AJ19                  | I        | S1VDD             | -     |

| SD1_RX7_N      | SerDes Receive Data (negative)             | AH20                  | I        | S1VDD             | -     |

| SD1_RX7_P      | SerDes Receive Data (positive)             | AJ20                  | I        | S1VDD             | -     |

| SD1_TX0_N      | SerDes Transmit Data (negative)            | AF10                  | 0        | X1VDD             | -     |

| SD1_TX0_P      | SerDes Transmit Data (positive)            | AE10                  | 0        | X1VDD             | -     |

| SD1_TX1_N      | SerDes Transmit Data (negative)            | AF11                  | 0        | X1VDD             | -     |

| SD1_TX1_P      | SerDes Transmit Data (positive)            | AE11                  | 0        | X1VDD             | -     |

| SD1_TX2_N      | SerDes Transmit Data (negative)            | AF13                  | 0        | X1VDD             | -     |

| SD1_TX2_P      | SerDes Transmit Data (positive)            | AE13                  | 0        | X1VDD             | -     |

| SD1_TX3_N      | SerDes Transmit Data (negative)            | AF14                  | 0        | X1VDD             | -     |

| SD1_TX3_P      | SerDes Transmit Data (positive)            | AE14                  | 0        | X1VDD             | -     |

| SD1_TX4_N      | SerDes Transmit Data (negative)            | AF16                  | 0        | X1VDD             | -     |

| SD1_TX4_P      | SerDes Transmit Data (positive)            | AE16                  | 0        | X1VDD             | -     |

| SD1_TX5_N      | SerDes Transmit Data (negative)            | AF17                  | 0        | X1VDD             | _     |

| SD1_TX5_P      | SerDes Transmit Data (positive)            | AE17                  | 0        | X1VDD             | -     |

| SD1_TX6_N      | SerDes Transmit Data (negative)            | AF19                  | 0        | X1VDD             | -     |

| SD1_TX6_P      | SerDes Transmit Data (positive)            | AE19                  | 0        | X1VDD             | -     |

| SD1_TX7_N      | SerDes Transmit Data (negative)            | AF20                  | 0        | X1VDD             | _     |

Table 2-1. Pinout List (Continued)

| Signal                                                           | Signal description                   | Package pin<br>number | Pin type | Power supply | Notes |

|------------------------------------------------------------------|--------------------------------------|-----------------------|----------|--------------|-------|

| SD1_TX7_P                                                        | SerDes Transmit Data (positive)      | AE20                  | 0        | X1VDD        | ı     |

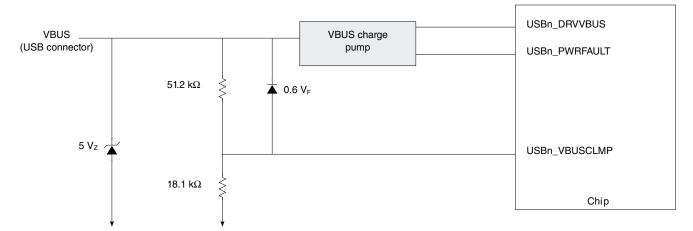

|                                                                  | USB PHY 1 & 2                        |                       |          |              |       |

| USB1_DRVVBUS                                                     | USB PHY Digital signal – Drive VBUS  | G6                    | 0        | USB_HVDD     | -     |

| USB1_PWRFAULT                                                    | USB PHY Digital signal – Power Fault | G5                    | I        | USB_HVDD     | -     |

| USB1_UDM                                                         | USB PHY Data Minus                   | G2                    | Ю        | USB_HVDD     | -     |

| USB1_UDP                                                         | USB PHY Data Plus                    | G1                    | Ю        | USB_HVDD     | -     |

| USB1_UID                                                         | USB PHY ID Detect                    | G4                    | I        | USB_OVDD     | _     |

| USB1_VBUSCLMP                                                    | USB PHY VBUS                         | F4                    | I        | USB_HVDD     | -     |

| USB2_DRVVBUS                                                     | USB PHY Digital signal – Drive VBUS  | K5                    | 0        | USB_HVDD     | _     |

| USB2_PWRFAULT                                                    | USB PHY Digital signal – Power Fault | J5                    | I        | USB_HVDD     | _     |

| USB2_UDM                                                         | USB PHY Data Minus                   | J2                    | Ю        | USB_HVDD     | -     |

| USB2_UDP                                                         | USB PHY Data Plus                    | J1                    | Ю        | USB_HVDD     | -     |

| USB2_UID                                                         | USB PHY ID Detect                    | J4                    | I        | USB_OVDD     | -     |

| USB2_VBUSCLMP                                                    | USB PHY VBUS                         | K4                    | I        | USB_HVDD     | -     |

| USB_IBIAS_REXT                                                   | USB PHY Impedance Calibration        | H4                    | Ю        | USB_OVDD     | (20)  |

|                                                                  | IEEE1588                             |                       |          |              |       |

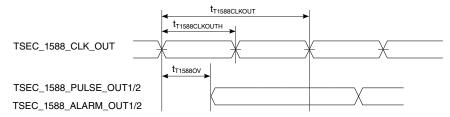

| TSEC_1588_ALARM_OUT1/GPIO3_03                                    | Alarm Out 1                          | AG5                   | 0        | LVDD         | (1)   |

| TSEC_1588_ALARM_OUT2/GPIO3_04/EMI1_MDC                           | Alarm Out 2                          | AD7                   | 0        | LVDD         | (1)   |

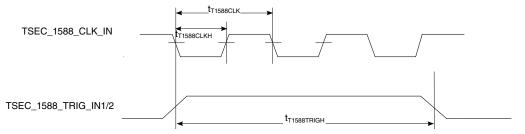

| TSEC_1588_CLK_IN/GPIO3_00                                        | Clock In                             | AD8                   | I        | LVDD         | (1)   |

| TSEC_1588_CLK_OUT/GPIO3_05                                       | Clock Out                            | AE7                   | 0        | LVDD         | (1)   |

| TSEC_1588_PULSE_OUT1/GPIO3_06                                    | Pulse Out 1                          | AF6                   | 0        | LVDD         | (1)   |

| TSEC_1588_PULSE_OUT2/GPIO3_07                                    | Pulse Out 2                          | AE8                   | 0        | LVDD         | (1)   |

| TSEC_1588_TRIG_IN1/GPIO3_01                                      | Trigger In 1                         | AC6                   | I        | LVDD         | (1)   |

| TSEC_1588_TRIG_IN2/GPIO3_02/EMI1_MDIO                            | Trigger In 2                         | AF5                   | 1        | LVDD         | (1)   |

|                                                                  | Ethernet Management Interface 1      |                       |          |              |       |

| EMI1_MDC                                                         | Management Data Clock                | AJ3                   | 0        | L1VDD        | -     |

| EMI1_MDC/TSEC_1588_ALARM_OUT2/GPIO3_04                           | Management Data Clock                | AD7                   | 0        | LVDD         | (1)   |

| EMI1_MDIO                                                        | Management Data In/Out               | AJ4                   | 10       | L1VDD        | -     |

| EMI1_MDIO/TSEC_1588_TRIG_IN2/GPIO3_02                            | Management Data In/Out               | AF5                   | Ю        | LVDD         | -     |

|                                                                  | Ethernet controller 1 and GPIO       |                       |          |              |       |

| EC1_COL/GPIO3_10/MII_COL/MAC2_MII_COL                            | Collison Detect                      | AD1                   | Ю        | L1VDD        | _     |

| EC1_GTX_CLK/GPIO3_16/MII_TX_CLK/MAC2_GTX_CLK/<br>MAC2_MII_TX_CLK | Transmit Clock Out                   | AG3                   | 0        | L1VDD        | (1)   |

| EC1_GTX_CLK125/GPIO3_17/MII_CRS/<br>MAC2_GTX_CLK125/MAC2_MII_CRS | Reference Clock                      | AH3                   | I        | L1VDD        | (1)   |

| EC1_RXD0/GPIO3_21/MII_RXD0/MAC2_RXD0/<br>MAC2_MII_RXD0           | Receive Data                         | AG2                   | I        | L1VDD        | (1)   |

| EC1_RXD1/GPIO3_20/MII_RXD1/MAC2_RXD1/<br>MAC2_MII_RXD1           | Receive Data                         | AG1                   | I        | L1VDD        | (1)   |

| EC1_RXD2/GPIO3_19/MII_RXD2/MAC2_RXD2/<br>MAC2_MII_RXD2           | Receive Data                         | AF1                   | I        | L1VDD        | (1)   |

| EC1_RXD3/GPIO3_18/MII_RXD3/MAC2_RXD3/<br>MAC2_MII_RXD3           | Receive Data                         | AE2                   | 1        | L1VDD        | (1)   |

Table 2-1.Pinout List (Continued)

| Signal                                                         | Signal description                                                    | Package pin<br>number | Pin type | Power supply | Notes   |

|----------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|----------|--------------|---------|

| EC1_RX_CLK/GPIO3_23/MII_RX_CLK/MAC2_RX_CLK/<br>MAC2_MII_RX_CLK | Receive Clock                                                         | AE1                   | I        | L1VDD        | (1)     |

| EC1_RX_CTL/GPIO3_22/MII_RX_DV/MAC2_RX_CTL/<br>MAC2_MII_RX_DV   | Receive Data Valid                                                    | AH2                   | I        | L1VDD        | (1)     |

| EC1_RX_ER/GPIO3_09/MII_RX_ER/MAC2_MII_RX_ER                    | Receive Error                                                         | AD2                   | Ю        | L1VDD        | _       |

| EC1_TXD0/GPIO3_14/MII_TXD0/MAC2_TXD0/<br>MAC2_MII_TXD0         | Transmit Data                                                         | AF3                   | 0        | L1VDD        | (1)     |

| EC1_TXD1/GPIO3_13/MII_TXD1/MAC2_TXD1/<br>MAC2_MII_TXD1         | Transmit Data                                                         | AF4                   | 0        | L1VDD        | (1)     |

| EC1_TXD2/GPIO3_12/MII_TXD2/MAC2_TXD2/<br>MAC2_MII_TXD2         | Transmit Data                                                         | AE3                   | 0        | L1VDD        | (1)     |

| EC1_TXD3/GPIO3_11/MII_TXD3/MAC2_TXD3/<br>MAC2_MII_TXD3         | Transmit Data                                                         | AD3                   | 0        | L1VDD        | (1)     |

| EC1_TX_CTL/GPIO3_15/MII_TX_EN/MAC2_TX_CTL/<br>MAC2_MII_TX_EN   | Transmit Enable                                                       | AG4                   | 0        | L1VDD        | (1)(14) |

| EC1_TX_ER/GPIO3_08/MII_TX_ER/MAC2_MII_TX_ER                    | Transmit Error                                                        | AD4                   | Ю        | L1VDD        | (14)    |

|                                                                | Ethernet controller 2 and GPIO                                        |                       |          |              | •       |

| EC2_GTX_CLK/GPIO4_28                                           | Transmit Clock Out                                                    | AF8                   | 0        | LVDD         | (1)     |

| EC2_GTX_CLK125/GPIO4_29                                        | Reference Clock                                                       | AD6                   | I        | LVDD         | (1)     |

| EC2_RXD0/GPIO3_31                                              | Receive Data                                                          | AJ8                   | I        | LVDD         | (1)     |

| EC2_RXD1/GPIO3_30                                              | Receive Data                                                          | AH7                   | I        | LVDD         | (1)     |

| EC2_RXD2/GPIO3_29                                              | Receive Data                                                          | AJ7                   | I        | LVDD         | (1)     |

| EC2_RXD3/GPIO3_28                                              | Receive Data                                                          | AJ6                   | I        | LVDD         | (1)     |

| EC2_RX_CLK/GPIO4_31                                            | Receive Clock                                                         | AJ5                   | I        | LVDD         | (1)     |

| EC2_RX_CTL/GPIO4_30                                            | Receive Data Valid                                                    | AH8                   | I        | LVDD         | (1)     |

| EC2_TXD0/GPIO3_27                                              | Transmit Data                                                         | AF7                   | 0        | LVDD         | (1)     |

| EC2_TXD1/GPIO3_26                                              | Transmit Data                                                         | AG7                   | 0        | LVDD         | (1)     |

| EC2_TXD2/GPIO3_25                                              | Transmit Data                                                         | AG6                   | 0        | LVDD         | (1)     |

| EC2_TXD3/GPIO3_24                                              | Transmit Data                                                         | AH5                   | 0        | LVDD         | (1)     |

| EC2_TX_CTL/GPIO4_27                                            | Transmit Enable                                                       | AG8                   | 0        | LVDD         | (1)(14) |

|                                                                | DSYSCLK                                                               |                       | 11       |              |         |

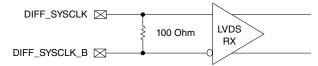

| DIFF_SYSCLK                                                    | "Single Oscillator Source" Reference<br>Clock Differential (positive) | H14                   | I        | O1VDD        | (18)    |

| DIFF_SYSCLK_B                                                  | "Single Oscillator Source" Reference<br>Clock Differential (negative) | G14                   | I        | O1VDD        | (18)    |

|                                                                | USB Clocking                                                          |                       |          |              |         |

| USBCLK                                                         | USB PHY Clock In                                                      | G8                    | I        | O1VDD        | (17)    |

|                                                                | I2C 3 & 4                                                             |                       | <u>I</u> | 1            | 1       |

| IIC3_SCL/GPIO4_00                                              | Serial Clock                                                          | W2                    | Ю        | DVDD         | (7)(8)  |

| IIC3_SDA/GPIO4_01                                              | Serial Data                                                           | Y3                    | Ю        | DVDD         | (7)(8)  |

| IIC4_SCL/GPIO4_02/EVT5_B/DIU_HSYNC                             | Serial Clock                                                          | AB3                   | IO       | DVDD         | (7)(8)  |

| IIC4_SDA/GPIO4_03/EVT6_B/DIU_VSYNC                             | Serial Data                                                           | AC3                   | Ю        | DVDD         | (7)(8)  |

| <del></del>                                                    | DMA                                                                   |                       | I        | 1            | .1      |

| DMA1_DACK0_B/GPIO4_05/TDM_TFS                                  | DMA1 channel 0 acknowledge                                            | V5                    | 0        | DVDD         | (1)     |

Table 2-1. Pinout List (Continued)

| Signal                                                             | Signal description         | Package pin<br>number | Pin type | Power supply | Notes  |

|--------------------------------------------------------------------|----------------------------|-----------------------|----------|--------------|--------|

| DMA1_DDONE0_B/GPIO4_06/TDM_TCK                                     | DMA1 channel 0 done        | T5                    | 0        | DVDD         | (1)    |

| DMA1_DREQ0_B/GPIO4_04/TDM_TXD                                      | DMA1 channel 0 request     | R5                    | I        | DVDD         | (1)    |

| DMA2_DACK0_B/GPIO4_08/EVT7_B/TDM_RFS                               | DMA2 channel 0 acknowledge | AB5                   | 0        | DVDD         | (1)    |

| DMA2_DDONE0_B/GPIO4_09/EVT8_B/TDM_RCK                              | DMA2 channel 0 done        | AA5                   | 0        | DVDD         | (1)    |

| DMA2_DREQ0_B/GPIO4_07/TDM_RXD                                      | DMA2 channel 0 request     | W5                    | I        | DVDD         | (1)    |

|                                                                    | QE_TDM                     |                       |          | 1            |        |

| <b>CLK09</b> /GPIO4_15/BRGO2/DIU_D10                               | External Clock             | R4                    | I        | DVDD         | (1)    |

| CLK10/GPIO4_22/BRGO3/DIU_D11                                       | External Clock             | R3                    | ı        | DVDD         | (1)    |

| CLK11/GPIO4_16/BRGO4/DIU_DE                                        | External Clock             | P4                    | ı        | DVDD         | (1)    |

| CLK12/GPIO4_23/BRGO1/DIU_CLK_OUT                                   | External Clock             | N4                    | I        | DVDD         | (1)(24 |

| TDMA_RQ/GPIO4_14/UC1_CDB_RXER/DIU_D4                               | Request                    | T2                    | 0        | DVDD         | (1)    |

| TDMA_RSYNC/GPIO4_11/UC1_CTSB_RXDV/DIU_D1                           | Receive Sync               | V1                    | ı        | DVDD         | (1)    |

| TDMA_RXD/GPIO4_10/UC1_RXD7/DIU_D0/TDMA_TXD                         | Receive Data               | V2                    |          | DVDD         | (1)    |

| TDMA_TSYNC/GPIO4_13/UC1_RTSB_TXEN/DIU_D3                           | Transmit Sync              | T1                    |          | DVDD         | (1)    |

| TDMA_TXD/GPIO4_12/UC1_TXD7/DIU_D2/ TDMA_RXD_EXC                    | Transmit Data              | U1                    | 0        | DVDD         | (1)    |

| TDMB_RQ/GPIO4_21/UC3_CDB_RXER/DIU_D9                               | Request                    | T4                    | 0        | DVDD         | (1)    |

| TDMB_RSYNC/GPIO4_18/UC3_CTSB_RXDV/DIU_D6                           | Receive Sync               | U3                    | ı        | DVDD         | (1)    |

| TDMB_RXD/GPIO4_17/UC3_RXD7/DIU_D5/TDMB_TXD                         | Receive Data               | V4                    | ı        | DVDD         | (1)    |

| TDMB_TSYNC/GPIO4_20/UC3_RTSB_TXEN/DIU_D8                           | Transmit Sync              | Т3                    | ı        | DVDD         | (1)    |

| TDMB_TXD/GPIO4_19/UC3_TXD7/DIU_D7/<br>TDMB_RXD_EXC                 | Transmit Data              | U4                    | 0        | DVDD         | (1)    |

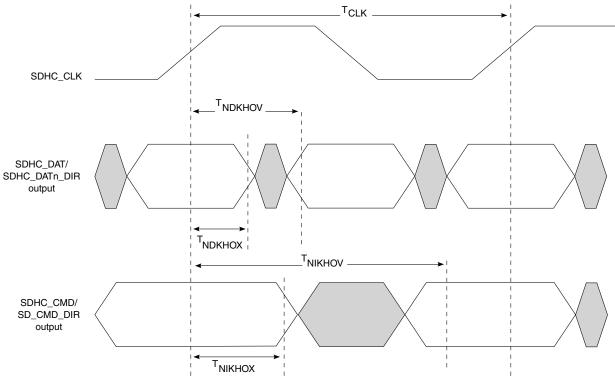

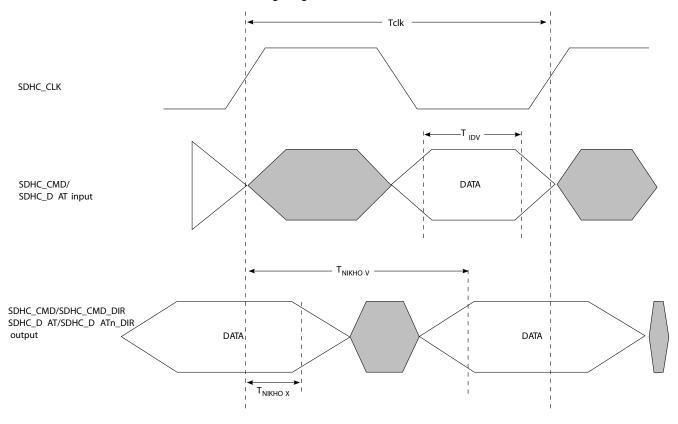

| 1                                                                  | eSDHC                      |                       |          |              |        |

| SDHC_CD_B/GPIO4_24                                                 | SDHC Card Detect           | M5                    | ı        | CVDD         | (1)    |

| SDHC_CLK/GPIO2_09                                                  | Host to Card Clock         | L1                    | Ю        | EVDD         | _      |

| SDHC_CLK_SYNC_IN/IRQ10/GPIO1_30                                    | Clock Sync                 | M4                    | ı        | CVDD         | (1)    |

| SDHC_CLK_SYNC_OUT/SPI_CS3_B/GPIO2_03/<br>SDHC_DAT7/SDHC_DAT123_DIR | Clock Sync                 | P3                    | 0        | CVDD         | (1)    |

| SDHC_CMD/GPIO2_04                                                  | Command/Response           | L3                    | Ю        | EVDD         | -      |

| SDHC_CMD_DIR/ <b>SPI_CS1_B</b> /GPIO2_01/SDHC_DAT5                 | CMD direction control      | N2                    | 0        | CVDD         | (1)    |

| SDHC_DAT0/GPIO2_05                                                 | Data                       | M2                    | Ю        | EVDD         | -      |

| SDHC_DAT0_DIR/ <b>SPI_CS2_B</b> /GPIO2_02/SDHC_DAT6                | Data                       | N3                    | 0        | CVDD         | (1)    |

| SDHC_DAT1/GPIO2_06                                                 | Data                       | L4                    | Ю        | EVDD         | _      |

| SDHC_DAT123_DIR/SPI_CS3_B/GPIO2_03/SDHC_DAT7/<br>SDHC_CLK_SYNC_OUT | Data                       | P3                    | 0        | CVDD         | (1)    |

| SDHC_DAT2/GPIO2_07                                                 | Data                       | M3                    | Ю        | EVDD         | -      |

| SDHC_DAT3/GPIO2_08                                                 | Data                       | M1                    | Ю        | EVDD         | -      |

| SDHC_DAT4/ <b>SPI_CS0_B</b> /GPIO2_00                              | Data                       | N1                    | Ю        | CVDD         | -      |

| SDHC_DAT5/ <b>SPI_CS1_B</b> /GPIO2_01/SDHC_CMD_DIR                 | Data                       | N2                    | Ю        | CVDD         | _      |

| SDHC_DAT6/ <b>SPI_CS2_B</b> /GPIO2_02/SDHC_DAT0_DIR                | Data                       | N3                    | Ю        | CVDD         | _      |

| SDHC_DAT7/SPI_CS3_B/GPIO2_03/SDHC_DAT123_DIR/<br>SDHC_CLK_SYNC_OUT | Data                       | P3                    | Ю        | CVDD         | _      |

Table 2-1. Pinout List (Continued)

| Signal                                   | Signal description                  | Package pin<br>number | Pin type | Power supply | Notes   |

|------------------------------------------|-------------------------------------|-----------------------|----------|--------------|---------|

| SDHC_VS/IRQ03/GPIO1_23                   | Voltage Select                      | E1                    | Ю        | O1VDD        | -       |

| SDHC_WP/GPIO4_25                         | SDHC Write Protect                  | N5                    | I        | CVDD         | (1)     |

|                                          | Power-On-Reset Configuration        |                       |          |              |         |

| cfg_dram_type/ <b>IFC_A21</b>            | Power-On-Reset Configuration Signal | D8                    | I        | OVDD         | (1)(4)  |

| cfg_eng_use0/ <b>IFC_WE0_B</b>           | Power-On-Reset Configuration Signal | E13                   | I        | OVDD         | (1)(21) |

| cfg_eng_use1/ <b>IFC_OE_B</b>            | Power-On-Reset Configuration Signal | E15                   | I        | OVDD         | (1)(21) |

| cfg_eng_use2/ <b>IFC_WP0_B</b>           | Power-On-Reset Configuration Signal | G17                   | I        | OVDD         | (1)     |

| cfg_gpinput0/ <b>IFC_AD00</b>            | Power-On-Reset Configuration Signal | B4                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput1/ <b>IFC_AD01</b>            | Power-On-Reset Configuration Signal | C5                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput2/ <b>IFC_AD02</b>            | Power-On-Reset Configuration Signal | B5                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput3/ <b>IFC_AD03</b>            | Power-On-Reset Configuration Signal | C6                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput4/ <b>IFC_AD04</b>            | Power-On-Reset Configuration Signal | B6                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput5/ <b>IFC_AD05</b>            | Power-On-Reset Configuration Signal | В7                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput6/ <b>IFC_AD06</b>            | Power-On-Reset Configuration Signal | C8                    | I        | OVDD         | (1)(4)  |

| cfg_gpinput7/ <b>IFC_AD07</b>            | Power-On-Reset Configuration Signal | B8                    | I        | OVDD         | (1)(4)  |

| cfg_ifc_te/IFC_TE                        | Power-On-Reset Configuration Signal | C14                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src0/ <b>IFC_AD08</b>            | Power-On-Reset Configuration Signal | C9                    | I        | OVDD         | (1)(4)  |

| cfg_rcw_src1/ <b>IFC_AD09</b>            | Power-On-Reset Configuration Signal | В9                    | I        | OVDD         | (1)(4)  |

| cfg_rcw_src2/ <b>IFC_AD10</b>            | Power-On-Reset Configuration Signal | B10                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src3/IFC_AD11                    | Power-On-Reset Configuration Signal | C11                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src4/IFC_AD12                    | Power-On-Reset Configuration Signal | B11                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src5/ <b>IFC_AD13</b>            | Power-On-Reset Configuration Signal | C12                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src6/ <b>IFC_AD14</b>            | Power-On-Reset Configuration Signal | B12                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src7/ <b>IFC_AD15</b>            | Power-On-Reset Configuration Signal | B13                   | I        | OVDD         | (1)(4)  |

| cfg_rcw_src8/IFC_CLE                     | Power-On-Reset Configuration Signal | G16                   | I        | OVDD         | (1)(4)  |

|                                          | General Purpose Input/Output        |                       | <u> </u> |              |         |

| GPIO1_09/IFC_CS4_B                       | General Purpose Input/Output        | F17                   | Ю        | OVDD         | _       |

| GPIO1_10/IFC_CS5_B                       | General Purpose Input/Output        | D17                   | Ю        | OVDD         | _       |

| GPIO1_11/ <b>IFC_CS6_B</b>               | General Purpose Input/Output        | E18                   | Ю        | OVDD         | -       |

| GPIO1_12/IFC_CS7_B                       | General Purpose Input/Output        | D19                   | Ю        | OVDD         | -       |

| GPO1_13/ <b>ASLEEP</b>                   | General Purpose Input/Output        | C2                    | 0        | O1VDD        | (1)     |

| GPIO1_14/RTC                             | General Purpose Input/Output        | C17                   | Ю        | OVDD         | -       |

| GPIO1_15/UART1_SOUT                      | General Purpose Input/Output        | AB2                   | Ю        | DVDD         | -       |

| GPIO1_16/UART2_SOUT                      | General Purpose Input/Output        | AB4                   | Ю        | DVDD         | _       |

| GPIO1_17/UART1_SIN                       | General Purpose Input/Output        | AB1                   | Ю        | DVDD         | _       |

| GPIO1_18/UART2_SIN                       | General Purpose Input/Output        | Y4                    | Ю        | DVDD         | _       |

| GPIO1_19/ <b>UART1_RTS_B</b> /UART3_SOUT | General Purpose Input/Output        | AA1                   | Ю        | DVDD         | -       |

| GPIO1_20/ <b>UART2_RTS_B</b> /UART4_SOUT | General Purpose Input/Output        | W4                    | Ю        | DVDD         | -       |

| GPIO1_21/UART1_CTS_B/UART3_SIN           | General Purpose Input/Output        | AA2                   | Ю        | DVDD         | _       |

| GPIO1_22/UART2_CTS_B/UART4_SIN           | General Purpose Input/Output        | AA4                   | IO       | DVDD         | _       |

Table 2-1. Pinout List (Continued)

| Signal                                                             | Signal description           | Package pin<br>number | Pin type | Power supply | Notes |

|--------------------------------------------------------------------|------------------------------|-----------------------|----------|--------------|-------|

| GPIO1_23/IRQ03/SDHC_VS                                             | General Purpose Input/Output | E1                    | Ю        | O1VDD        |       |

| GPIO1_24/ <b>IRQ04</b>                                             | General Purpose Input/Output | E4                    | Ю        | O1VDD        | -     |

| GPIO1_25/ <b>IRQ05</b>                                             | General Purpose Input/Output | E5                    | Ю        | O1VDD        | -     |

| GPIO1_26/ <b>IRQ06</b>                                             | General Purpose Input/Output | AC4                   | 10       | L1VDD        | -     |

| GPIO1_27/IRQ07                                                     | General Purpose Input/Output | AE5                   | 10       | L1VDD        | _     |

| GPIO1_28/IRQ08                                                     | General Purpose Input/Output | AC1                   | 10       | L1VDD        | _     |

| GPIO1_29/ <b>IRQ09</b>                                             | General Purpose Input/Output | AD5                   | 10       | L1VDD        | _     |

| GPIO1_30/IRQ10/SDHC_CLK_SYNC_IN                                    | General Purpose Input/Output | M4                    | 10       | CVDD         | -     |

| GPIO1_31/ <b>IRQ11</b>                                             | General Purpose Input/Output | V3                    | 10       | DVDD         | -     |

| GPIO2_00/ <b>SPI_CS0_B</b> /SDHC_DAT4                              | General Purpose Input/Output | N1                    | Ю        | CVDD         | _     |

| GPIO2_01/SPI_CS1_B/SDHC_DAT5/SDHC_CMD_DIR                          | General Purpose Input/Output | N2                    | 10       | CVDD         | -     |

| GPIO2_02/ <b>SPI_CS2_B</b> /SDHC_DAT6/SDHC_DAT0_DIR                | General Purpose Input/Output | N3                    | Ю        | CVDD         | _     |

| GPIO2_03/SPI_CS3_B/SDHC_DAT7/SDHC_DAT123_DIR/<br>SDHC_CLK_SYNC_OUT | General Purpose Input/Output | P3                    | Ю        | CVDD         | _     |

| GPIO2_04/SDHC_CMD                                                  | General Purpose Input/Output | L3                    | 10       | EVDD         | -     |

| GPIO2_05/SDHC_DAT0                                                 | General Purpose Input/Output | M2                    | 10       | EVDD         | _     |

| GPIO2_06/SDHC_DAT1                                                 | General Purpose Input/Output | L4                    | 10       | EVDD         | -     |

| GPIO2_07/SDHC_DAT2                                                 | General Purpose Input/Output | M3                    | 10       | EVDD         | _     |

| GPIO2_08/SDHC_DAT3                                                 | General Purpose Input/Output | M1                    | Ю        | EVDD         | -     |

| GPIO2_09/SDHC_CLK                                                  | General Purpose Input/Output | L1                    | Ю        | EVDD         | -     |

| GPIO2_10/IFC_CS1_B                                                 | General Purpose Input/Output | F15                   | Ю        | OVDD         | -     |

| GPIO2_11/IFC_CS2_B                                                 | General Purpose Input/Output | E16                   | Ю        | OVDD         | -     |

| GPIO2_12/IFC_CS3_B                                                 | General Purpose Input/Output | D16                   | Ю        | OVDD         | -     |

| GPIO2_13/IFC_PAR0                                                  | General Purpose Input/Output | D15                   | Ю        | OVDD         | -     |

| GPIO2_14/IFC_PAR1                                                  | General Purpose Input/Output | D14                   | Ю        | OVDD         | -     |

| GPIO2_15/IFC_PERR_B                                                | General Purpose Input/Output | F14                   | Ю        | OVDD         |       |

| GPIO2_25/IFC_A25/IFC_WP1_B                                         | General Purpose Input/Output | D10                   | Ю        | OVDD         | -     |

| GPIO2_26/ <b>IFC_A26</b> /IFC_WP2_B                                | General Purpose Input/Output | F11                   | Ю        | OVDD         | -     |

| GPIO2_27/ <b>IFC_A27</b> /IFC_WP3_B                                | General Purpose Input/Output | D11                   | Ю        | OVDD         | -     |

| GPIO2_28/ <b>IFC_A28</b>                                           | General Purpose Input/Output | E11                   | Ю        | OVDD         | -     |

| GPIO2_29/ <b>IFC_A29</b> /IFC_RB2_B                                | General Purpose Input/Output | D12                   | Ю        | OVDD         | -     |

| GPIO2_30/ <b>IFC_A30</b> /IFC_RB3_B                                | General Purpose Input/Output | E12                   | Ю        | OVDD         | -     |

| GPIO2_31/ <b>IFC_A31</b> /IFC_RB4_B                                | General Purpose Input/Output | F12                   | Ю        | OVDD         | -     |

| GPIO3_00/TSEC_1588_CLK_IN                                          | General Purpose Input/Output | AD8                   | Ю        | LVDD         | _     |

| GPIO3_01/TSEC_1588_TRIG_IN1                                        | General Purpose Input/Output | AC6                   | Ю        | LVDD         | _     |

| GPIO3_02/TSEC_1588_TRIG_IN2/EMI1_MDIO                              | General Purpose Input/Output | AF5                   | Ю        | LVDD         | _     |

| GPIO3_03/TSEC_1588_ALARM_OUT1                                      | General Purpose Input/Output | AG5                   | Ю        | LVDD         | -     |

| GPIO3_04/TSEC_1588_ALARM_OUT2/EMI1_MDC                             | General Purpose Input/Output | AD7                   | Ю        | LVDD         | _     |

| GPIO3_05/TSEC_1588_CLK_OUT                                         | General Purpose Input/Output | AE7                   | Ю        | LVDD         | _     |

| GPIO3_06/TSEC_1588_PULSE_OUT1                                      | General Purpose Input/Output | AF6                   | Ю        | LVDD         | _     |

Table 2-1. Pinout List (Continued)

| Signal                                                                    | Signal description           | Package pin<br>number | Pin type | Power supply | Notes |

|---------------------------------------------------------------------------|------------------------------|-----------------------|----------|--------------|-------|

| GPIO3_07/TSEC_1588_PULSE_OUT2                                             | General Purpose Input/Output | AE8                   | Ю        | LVDD         | -     |

| GPIO3_08/ <b>EC1_TX_ER</b> /MII_TX_ER/MAC2_MII_TX_ER                      | General Purpose Input/Output | AD4                   | 10       | L1VDD        | -     |

| GPIO3_09/EC1_RX_ER/MII_RX_ER/MAC2_MII_RX_ER                               | General Purpose Input/Output | AD2                   | 10       | L1VDD        | -     |

| GPIO3_10/EC1_COL/MII_COL/MAC2_MII_COL                                     | General Purpose Input/Output | AD1                   | 10       | L1VDD        | -     |

| GPIO3_11/EC1_TXD3/MII_TXD3/MAC2_TXD3/<br>MAC2_MII_TXD3                    | General Purpose Input/Output | AD3                   | Ю        | L1VDD        | -     |

| GPIO3_12/EC1_TXD2/MII_TXD2/MAC2_TXD2/<br>MAC2_MII_TXD2                    | General Purpose Input/Output | AE3                   | Ю        | L1VDD        | -     |

| GPIO3_13/EC1_TXD1/MII_TXD1/MAC2_TXD1/<br>MAC2_MII_TXD1                    | General Purpose Input/Output | AF4                   | Ю        | L1VDD        | -     |

| GPIO3_14/EC1_TXD0/MII_TXD0/MAC2_TXD0/<br>MAC2_MII_TXD0                    | General Purpose Input/Output | AF3                   | Ю        | L1VDD        | -     |

| GPIO3_15/ <b>EC1_TX_CTL</b> /MII_TX_EN/MAC2_TX_CTL/<br>MAC2_MII_TX_EN     | General Purpose Input/Output | AG4                   | Ю        | L1VDD        | -     |

| GPIO3_16/ <b>EC1_GTX_CLK</b> /MII_TX_CLK/<br>MAC2_GTX_CLK/MAC2_MII_TX_CLK | General Purpose Input/Output | AG3                   | Ю        | L1VDD        | _     |

| GPIO3_17/ <b>EC1_GTX_CLK125</b> /MII_CRS/<br>MAC2_GTX_CLK125/MAC2_MII_CRS | General Purpose Input/Output | AH3                   | Ю        | L1VDD        | -     |

| GPIO3_18/EC1_RXD3/MII_RXD3/MAC2_RXD3/<br>MAC2_MII_RXD3                    | General Purpose Input/Output | AE2                   | Ю        | L1VDD        | -     |

| GPIO3_19/EC1_RXD2/MII_RXD2/MAC2_RXD2/<br>MAC2_MII_RXD2                    | General Purpose Input/Output | AF1                   | Ю        | L1VDD        | -     |

| GPIO3_20/ <b>EC1_RXD1</b> /MII_RXD1/MAC2_RXD1/<br>MAC2_MII_RXD1           | General Purpose Input/Output | AG1                   | Ю        | L1VDD        | -     |

| GPIO3_21/ <b>EC1_RXD0</b> /MII_RXD0/MAC2_RXD0/<br>MAC2_MII_RXD0           | General Purpose Input/Output | AG2                   | Ю        | L1VDD        | -     |

| GPIO3_22/EC1_RX_CTL/MII_RX_DV/MAC2_RX_CTL/<br>MAC2_MII_RX_DV              | General Purpose Input/Output | AH2                   | Ю        | L1VDD        | -     |

| GPIO3_23/EC1_RX_CLK/MII_RX_CLK/MAC2_RX_CLK/<br>MAC2_MII_RX_CLK            | General Purpose Input/Output | AE1                   | Ю        | L1VDD        | -     |

| GPIO3_24/EC2_TXD3                                                         | General Purpose Input/Output | AH5                   | 10       | LVDD         | -     |

| GPIO3_25/EC2_TXD2                                                         | General Purpose Input/Output | AG6                   | 10       | LVDD         | -     |

| GPIO3_26/EC2_TXD1                                                         | General Purpose Input/Output | AG7                   | 10       | LVDD         | _     |

| GPIO3_27/EC2_TXD0                                                         | General Purpose Input/Output | AF7                   | 10       | LVDD         | _     |

| GPIO3_28/EC2_RXD3                                                         | General Purpose Input/Output | AJ6                   | 10       | LVDD         | _     |

| GPIO3_29/EC2_RXD2                                                         | General Purpose Input/Output | AJ7                   | 10       | LVDD         | _     |

| GPIO3_30/EC2_RXD1                                                         | General Purpose Input/Output | AH7                   | Ю        | LVDD         | -     |

| GPIO3_31/EC2_RXD0                                                         | General Purpose Input/Output | AJ8                   | Ю        | LVDD         | _     |

| GPIO4_00/ <b>IIC3_SCL</b>                                                 | General Purpose Input/Output | W2                    | Ю        | DVDD         | _     |

| GPIO4_01/IIC3_SDA                                                         | General Purpose Input/Output | Y3                    | 10       | DVDD         | _     |

| GPIO4_02/IIC4_SCL/EVT5_B/DIU_HSYNC                                        | General Purpose Input/Output | AB3                   | 10       | DVDD         | _     |

| GPIO4_03/IIC4_SDA/EVT6_B/DIU_VSYNC                                        | General Purpose Input/Output | AC3                   | Ю        | DVDD         | _     |

| GPIO4_04/DMA1_DREQ0_B/TDM_TXD                                             | General Purpose Input/Output | R5                    | 10       | DVDD         | _     |

| GPIO4_05/ <b>DMA1_DACK0_B</b> /TDM_TFS                                    | General Purpose Input/Output | V5                    | 10       | DVDD         | _     |

| GPIO4_06/ <b>DMA1_DDONE0_B</b> /TDM_TCK                                   | General Purpose Input/Output | T5                    | 10       | DVDD         | _     |

| GPIO4_07/ <b>DMA2_DREQ0_B</b> /TDM_RXD                                    | General Purpose Input/Output | W5                    | Ю        | DVDD         |       |

Table 2-1. Pinout List (Continued)

| Signal                                         | Signal description           | Package pin<br>number | Pin type | Power supply | Notes |

|------------------------------------------------|------------------------------|-----------------------|----------|--------------|-------|

| GPIO4_08/DMA2_DACK0_B/EVT7_B/TDM_RFS           | General Purpose Input/Output | AB5                   | 10       | DVDD         | -     |

| GPIO4_09/ <b>DMA2_DDONE0_B</b> /EVT8_B/TDM_RCK | General Purpose Input/Output | AA5                   | 10       | DVDD         | -     |

| GPIO4_10/TDMA_RXD/UC1_RXD7/DIU_D0              | General Purpose Input/Output | V2                    | 10       | DVDD         | _     |

| GPIO4_11/TDMA_RSYNC/UC1_CTSB_RXDV/DIU_D1       | General Purpose Input/Output | V1                    | 10       | DVDD         | -     |

| GPIO4_12/TDMA_TXD/UC1_TXD7/DIU_D2              | General Purpose Input/Output | U1                    | 10       | DVDD         | -     |

| GPIO4_13/TDMA_TSYNC/UC1_RTSB_TXEN/DIU_D3       | General Purpose Input/Output | T1                    | 10       | DVDD         | -     |

| GPIO4_14/TDMA_RQ/UC1_CDB_RXER/DIU_D4           | General Purpose Input/Output | T2                    | 10       | DVDD         | -     |

| GPIO4_15/ <b>CLK09</b> /BRGO2/DIU_D10          | General Purpose Input/Output | R4                    | 10       | DVDD         | -     |

| GPIO4_16/ <b>CLK11</b> /BRGO4/DIU_DE           | General Purpose Input/Output | P4                    | 10       | DVDD         | _     |

| GPIO4_17/TDMB_RXD/UC3_RXD7/DIU_D5              | General Purpose Input/Output | V4                    | 10       | DVDD         | _     |

| GPIO4_18/TDMB_RSYNC/UC3_CTSB_RXDV/DIU_D6       | General Purpose Input/Output | U3                    | 10       | DVDD         | _     |

| GPIO4_19/TDMB_TXD/UC3_TXD7/DIU_D7              | General Purpose Input/Output | U4                    | 10       | DVDD         | _     |

| GPIO4_20/TDMB_TSYNC/UC3_RTSB_TXEN/DIU_D8       | General Purpose Input/Output | Т3                    | Ю        | DVDD         | _     |

| GPIO4_21/TDMB_RQ/UC3_CDB_RXER/DIU_D9           | General Purpose Input/Output | T4                    | Ю        | DVDD         | _     |

| GPIO4_22/CLK10/BRGO3/DIU_D11                   | General Purpose Input/Output | R3                    | Ю        | DVDD         | -     |

| GPIO4_23/CLK12/BRGO1/DIU_CLK_OUT               | General Purpose Input/Output | N4                    | Ю        | DVDD         | -     |

| GPIO4_24/SDHC_CD_B                             | General Purpose Input/Output | M5                    | Ю        | CVDD         | _     |

| GPIO4_25/ <b>SDHC_WP</b>                       | General Purpose Input/Output | N5                    | Ю        | CVDD         | _     |

| GPIO4_27/EC2_TX_CTL                            | General Purpose Input/Output | AG8                   | 10       | LVDD         | _     |

| GPIO4_28/EC2_GTX_CLK                           | General Purpose Input/Output | AF8                   | Ю        | LVDD         | _     |

| GPIO4_29/EC2_GTX_CLK125                        | General Purpose Input/Output | AD6                   | Ю        | LVDD         | _     |

| GPIO4_30/EC2_RX_CTL                            | General Purpose Input/Output | AH8                   | Ю        | LVDD         | _     |

| GPIO4_31/EC2_RX_CLK                            | General Purpose Input/Output | AJ5                   | Ю        | LVDD         | -     |

|                                                | DIU                          |                       | 1        | 1            |       |

| DIU_CLK_OUT/ <b>CLK12</b> /GPIO4_23/BRGO1      | Pixel Clock                  | N4                    | 0        | DVDD         | (1)   |

| DIU_D0/TDMA_RXD/GPIO4_10/UC1_RXD7              | DIU Data                     | V2                    | 0        | DVDD         | (1)   |

| DIU_D1/TDMA_RSYNC/GPIO4_11/UC1_CTSB_RXDV       | DIU Data                     | V1                    | 0        | DVDD         | (1)   |

| DIU_D10/ <b>CLK09</b> /GPIO4_15/BRGO2          | DIU Data                     | R4                    | 0        | DVDD         | (1)   |

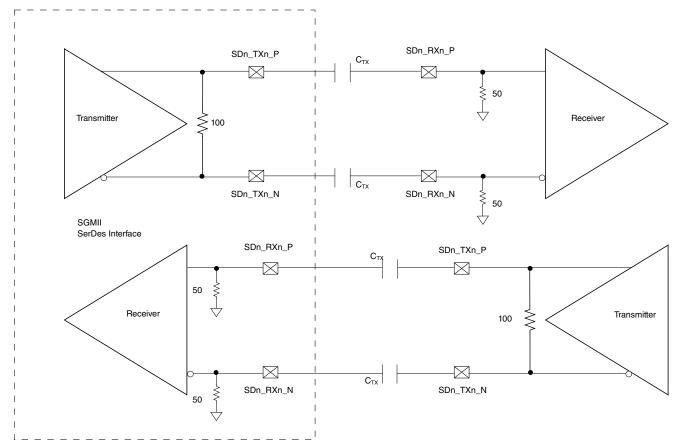

| DIU_D11/ <b>CLK10</b> /GPIO4_22/BRGO3          | DIU Data                     | R3                    | 0        | DVDD         | (1)   |