# Determining Valid Divide Ratios Using Peregrine PLL Frequency Synthesizers

## Introduction

The purpose of the N divider in a phase-locked loop (PLL) is to divide the high frequency of the VCO down to a more manageable frequency that the phase detector can process. Different architectures are available that use counters to scale the frequency. However, not every frequency can be realized due to restrictions with the counting registers. This application note describes how to determine which divide ratios are valid when using Peregrine Semiconductor's PLL frequency synthesizers.

## Summary

- A dual modulus prescaler cannot synthesize every frequency due to limitations with its architecture

- A selectable dual modulus prescaler with a lower modulus decreases the minimum continuous divide ratio and improves the frequency selectivity

- The valid divide ratio is further limited by the operational parameters of the noise shaping delta-sigma modulator of a fractional synthesizer

- Invalid divide ratios apply to M and A register values below N<sub>MIN</sub>. Above N<sub>MIN</sub> there is no limitation

### **Dual Modulus Prescaler**

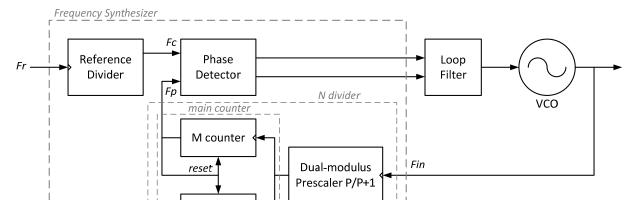

Frequency synthesizers can be integer-N or fractional-N depending on the design and requirements of the PLL. Both types of frequency synthesizers commonly use dual-modulus prescalers in the feedback (N) divider. Its architecture consists of a high frequency prescaler and two low frequency dividers as shown in *Figure 1*. The dual-modulus prescaler takes the high frequency of the VCO and divides it down to a more manageable lower frequency for the main counter. This configuration facilitates closer channel spacing with higher VCO frequency operation without losing the frequency resolution inherent in a single modulus N divider scheme.

modulus select

### Figure 1. Integer-N PLL Functional Block Diagram with a Dual Modulus Prescaler

The main counter chain then divides the prescaler output by an integer derived from the settings in the M and A counters. Programming the M counter with the minimum allowed value of "1" will result in a minimum M counter divide ratio of "2." Therefore, the output from the main counter chain ( $F_P$ ) is related to the VCO frequency ( $F_{IN}$ ) by:

$$F_{P} = F_{IN} / [P^{*}(M+1) + A]$$

(1)

A counter

where P is the lowest modulus value and

$$N = F_{\rm IN} / F_{\rm P} = P^* (M+1) + A$$

(2)

$M = N^{*} (1/P) - 1$  (3)

where the integer value of M is used, and

$$A = N - P^{*}(M + 1)$$

(4)

For applications support, please visit www.e2v-us.com

### Integer-N Valid Divide Ratios

A dual modulus prescaler cannot synthesize every divide ratio due to the counting algorithm of the M and A counters. In order to guarantee a contiguous division ratio in integer mode, the following conditions must be met:

$$A \le M + 1 \tag{5}$$

$N_{MIN} = P^2 - P \tag{6}$

The A counter can accept values as high as 15 when  $N \ge N_{MIN}$ , but in typical operation it will cycle from 0 to P - 1 in increments of M. Below  $N_{MIN}$ , some frequencies will not be attainable. If an invalid divide ratio is selected, the PLL may lock to the wrong frequency or lose lock completely.

As an example, for P = 10, contiguous channels will be achieved for N  $\ge$  90. But suppose a divide ratio of 45 is needed to achieve a specific operating frequency such as 2.25 GHz using a comparison frequency of 50 MHz. Equations (3) and (4) determine the required register values:

$$M = 45 * (1/10) - 1 = 3$$

A = 45 - 10 \* (3+1) = 5

Since the A  $\leq$  M + 1 requirement is not met, 45 results in an invalid divide ratio using the allocated frequency plan. The comparison frequency could be scaled to another value such as 30 MHz, which would raise the divide ratio to 75. (Note that when scaling the comparison frequency while using the same loop bandwidth and VCO frequency, the theoretical change of in-band phase noise will be 10 \* log (Fc1 / Fc2), where Fc1 is original and Fc2 the final frequency. Therefore, if Fc1 is 50 MHz and Fc2 is 30 MHz, the in-band floor noise will degrade by 2.2 dB.)

Lower contiguous divide ratios can be achieved by reducing the modulus value. Peregrine's next generation of PLL frequency synthesizers have selectable 5/6 and 10/11 dual-modulus prescalers. The 5/6 prescaler can achieve a minimum continuous divide ratio of 20. This would allow 45 to be a valid divide ratio in the previous example. Note that lowering the modulus requires the M and A counters to run at higher frequencies, which may exceed the limit of their capability. The maximum operating frequency of each prescaler mode is specified in the device datasheet.

### **Fractional-N Valid Divide Ratios**

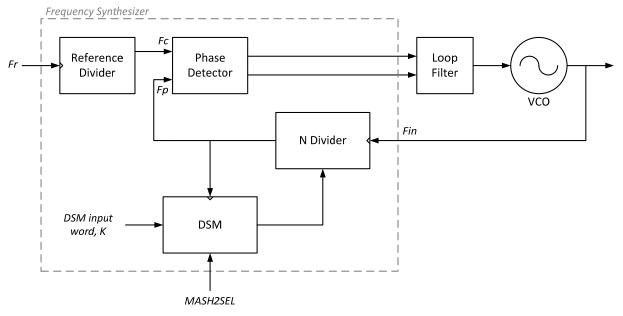

The integer-N frequency synthesizer is a widely used architecture, but its channel spacing or frequency step size is limited by the comparison frequency ( $F_c$ ). In order to achieve a smaller step size, it is necessary to lower the comparison frequency, which results in a higher division ratio for the PLL, an increased in-band phase noise, lower loop bandwidth and slower switching speed. Fractional-N synthesizers allow the PLL to operate with a higher reference frequency while realizing a fine step size by periodically modulating the division ratio between N and N+1, for example, such that the average value contains a fractional element. This is the fundamental operation of the Delta-Sigma Modulator (DSM).

One of the consequences of the DSM is its generation of fractional spurs due to the accumulation of random phase errors. Delta-sigma noise shaping techniques are applied to fractional-N synthesizers to shift unwanted spurs outside the bandwidth of the loop filter. However, the valid divide ratio is further limited by the delta-sigma modulator due to variation of the instantaneous division ratio around the average correct division ratio.

Peregrine's PLL frequency synthesizers use two Multi-stAge noise Shaping (MASH) decimation structures for reducing fractional spurs. MASH-1-1 mode is a 2nd order fractional dithering using four (2<sup>2</sup>) N values: N-1, N, N+1 and N+2. MASH-1-1-1 mode is a 3rd order fractional dithering using eight (2<sup>3</sup>) N values: N-3, N-2, N-1, N, N+1, N+2, N+3 and N+4. MASH-1-1-1 mode reduces fractional spurs but decreases the number of valid programming frequencies.

In order to guarantee a contiguous division ratio in fractional operation, the following conditions must be met:

| $A \leq M + 1$ | (7) |

|----------------|-----|

|                | (1) |

MASH-1-1 mode:

$N_{MIN} - 1 = (P^2 - P)$  (8)

MASH-1-1-1 mode:

$$N_{MIN} - 3 = (P^2 - P)$$

(9)

Consider for example P = 10/11 and N = 90 using MASH-1-1 noise shaping. Because the desired divide ratio is below the minimum N value of 91 from equation (8), all four divide ratios must be verified against equation (7) as shown in *Table 1*:

| N        | М | Α | A ≤ M + 1? |

|----------|---|---|------------|

| N-1 = 89 | 7 | 9 | invalid    |

| N = 90   | 8 | 0 | valid      |

| N+1 = 91 | 8 | 1 | valid      |

| N+2 = 92 | 8 | 2 | valid      |

Since the A  $\leq$  M + 1 requirement is not met for <u>all</u> four values N-1 thru N+1, 90 cannot be used. However, choosing a different comparison frequency or selecting a lower modulus (if applicable), as described for the integer operation, may also be considered to achieve the desired operating frequency.

#### Conclusion

A dual modulus prescaler offers divider programmability and allows the frequency synthesizer to operate at higher frequencies without losing frequency resolution. However, it cannot synthesize every frequency due to limitations with its architecture. Having the ability to select a lower modulus decreases the minimum continuous divide ratio and improves the frequency selectivity. Fractional-N frequency synthesizers, using delta-sigma noise shaping techniques to reduce spurs, introduce an additional factor which further limits the valid N availability. Avoiding invalid divide ratios are necessary to ensure that the PLL will remain locked under normal operation.

#### Sales Contact and Information

<u>Contact Information:</u> e2v ~ <u>http://www.e2v-us.com</u> ~ inquiries@e2v-us.com

<u>Advance Information</u>: The product is in a formative or design stage. The datasheet contains design target specifications for product development. Specifications and features may change in any manner without notice. <u>Preliminary Specification</u>: The datasheet contains preliminary data. Additional data may be added at a later date. Peregrine reserves the right to change specifications at any time without notice in order to supply the best possible product. <u>Predimitary Specifications</u>: The datasheet contains final data. In the event Peregrine decides to change the specifications, Peregrine will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

For applications support, please visit www.e2v-us.com

The information in this datasheet is believed to be reliable. However, Peregrine assumes no liability for the use of this information. Use shall be entirely at the user's own risk.

No patent rights or licenses to any circuits described in this datasheet are implied or granted to any third party. Peregrine's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Peregrine product could create a situation in which personal injury or death might occur. Peregrine assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

The Peregrine name, logo and UltraCMOS are registered trademarks, and HaRP is a trademark of Peregrine Semiconductor Corp. Peregrine products are protected under one or more of the following U.S. Patents: <u>http://patents.psemi.com</u>. All other trademarks and logos are the property of their respective owners.

Document No. DOC-57802-5 | UltraCMOS<sup>®</sup> RFIC Solutions

©2014–2015 Peregrine Semiconductor Corp. All rights reserved.